# **Basics of Electronics**

By

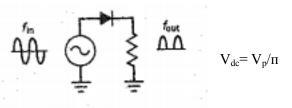

# Mr. Aniket Kumar

I TRANSFER

Assistant Professor, Department of Electronics & Communication Engineering Shobhit Institute of Engineering & Technology (Deemed to-be University) NH-58, Modipuram, Meerut – 250 110, India

# <u>Chapter-1</u> <u>Semiconductor</u>

#### Conductor, Semiconductor & Insulators

**Conductors:** Semiconductors are those materials whose electrical conductivity is vary high ,through these materials electricity pass easily .The valence band and the conduction band overlap each other i.e. their is no forbidden energy gap ( $E_g=0$ ). At absolute zero temperature ,large number of electrons remain in the conduction band. for example : copper , alluminium , gold etc.

**Semiconductors:** Semiconductors are those materials whose electrical conductivity is between conductors and insulators. The forbidden energy gap of a semiconductor is nearly same as insulator. The energy gap is narrower. The value of  $E_g = 1.1 \text{eV}$  for silicon crystal and  $E_g = 0.7 \text{eV}$  for germanium at ok. It can easily overcome due to thermal agitation or light. A semiconductor remains partially full valence band and partially full conduction band at the room temperature.

**Insulator:** Through these materials electricity cannot pass .Plastic, glass, wood etc are the examples of insulators. The valence band of these material remains full of electrons & the conduction band of these material remains empty. The forbidden energy gap between is widest i.e. is more than 10ev.

## **Intrinsic Semiconductors**

An intrinsic semiconductor is a pure semiconductors .When an external voltage is applied to the instrinsic semiconductor, the free electrons flow toward the +ve battery terminal and the holes flow toward the negative terminal.

#### Two types of flow

Two types of carrier flow exist in an intrinsic semiconductor. First, there is the flow of free electrons through larger orbits (conduction band). Second, there is the flow of holes through smaller orbits(valence band)

#### **Doping a Semiconductor**

Doping is the process of control addition of impurity in pure semi conductor, it increases the conductivity of a semiconductor. A doped semiconductor is called extrinsic semiconductor. When an intrinsic semiconductor is doped with pentavalent (doner) atoms, it has more free electrons then holes. When an intrinsic semiconductor is doped with trivalent (acceptor) atoms, it has more holes then free electrons.

#### Two types of extrinsic semiconductors

In an n-type semiconductor the free electrons are the majority carrier, and the holes are minority carriers. In a p-type semiconductor the holes are the majority carriers, and the free electrons are the minority carriers.

#### pn Junction

It is a border between p-type & n-type semiconductor. The pn- junction itself forms the most basic semiconductor device called semiconductor diode, thus semiconductor diode and pn junction are one and the same.

#### **Depletion layer**

In pn junction diode the the free electrons on n side tend to diffuse across the junction ,when free electrons enters the p region, the free electrons recombines with hole in p region, and due to which hole disappears and free electron becomes valence electron.

Each time an electron diffuses across a junction, it creates a pair of ions, +ve ion on n side and -ve ion on p side, these pair of ions at junction is called a dipole. As no. of dipoles builds up, empty charge region is created know as depletion region.

## Junction Potential width of depletion layer

Width of depletion layer is the distance measured from one side to the other side of the depletion region. Due to the presence of depletion region the electrons and holes do not i.e. depletion region acts as a barrier. Due to the presence of immobile +ve(n-side) and –ve (p-side) ions on opposite sides of the junction an electric field is created across the junction. This electric field is known as junction potential also known as barrier potential. The barrier potential for silicon is 0.7 volt whereas for germanium is 0.3 volt at  $25^{\circ}$ C.

#### Forward bias & Reverse bias

When an external voltage opposes the barrier potential, the diode is forward biased. If the applied voltage is greater than the barrier potential, the current flows. When an external voltage opposes the barrier potential, the diode is forward biased.

#### Diffusion of carriers in semiconductor : -

The movement of charge carriers from the region of high carrier concentration to the areas of low concentration, recombination of charge carriers occurs, the process is known as diffusion of carriers. The rate at which diffusion occurs depends on the velocity at which carriers move and on the distance between the carriers.

This diffusion current is proportional to the concentration gradient :

$$J_{nd} = q.D_{n}.\frac{\partial n}{\partial x}$$

$$J_{pd} = -q.D_{p}.\frac{\partial p}{\partial x}$$

Where  $D_n$  and  $D_p$  are the diffusion constant of p and n- type semiconductor, generally free electrons moves in conduction band & holes in valence band , valence band is more effected by electrostatic force so, we say mobility(it is the ease with which charge carriers flow) of electrons is higher then that of holes

The mobility of electron being higher than that of holes, the Einstein relationship shows that, for a given concentration gradient, the diffusion current for electrons is higher than the diffusion current for holes.

$$\frac{D_n}{\mu_n} = \frac{D_p}{\mu_p} = \frac{kT}{q}$$

## Work function in metals and semiconductor junction:-

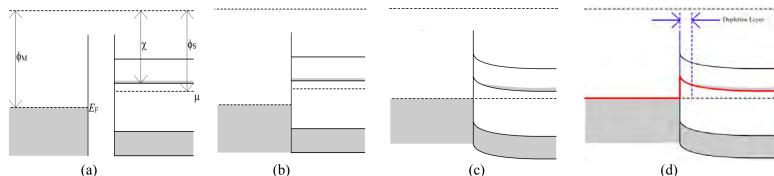

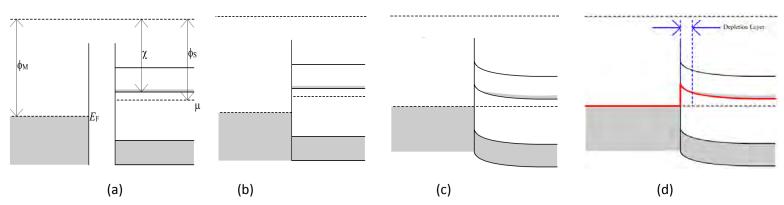

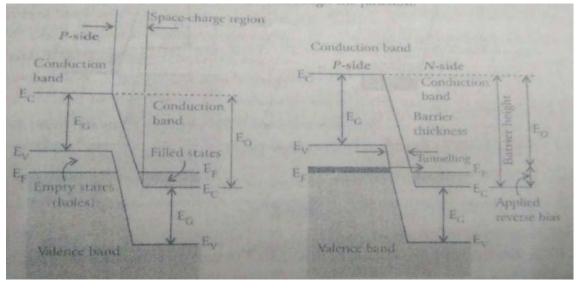

Energy required for an electron to move from Fermi level into the free space known as work function. The schematic below in fig. a shows a metal and an n-type semiconductor. The dashed line at the top represents the zero of energy of free space.

In fig. a, the work functions of metal & semi conductor denoted by  $\Phi_M \& \Phi_S$  resp.,  $E_F \& \mu$  indicates the fermi level of metal & semi conductor resp,  $\chi$  i.e. electron effinity.

When contact is made as shown in fig. b, electrons lower their energy by flowing from the semiconductor conduction band into the metal. This continues until the fermi energy level in the semiconductor as shown in fig. c reaches equilibrium with the fermi energy of the metal. The deformed band structure as shown in fig. d known as depletion layer forms a potential barrier.

## **The Energy Hill**

The barrier potential of a diode looks like an energy hill. Electrons attempting to cross the junction need to have enough energy to climb this hill. An external voltage source that forward-bais the diode gives electrons the energy required to pass through the depletion layer.

## **Barrier Potential & Temperature**

When the junction temperature increases, the depletion layer becomes narrow & the barrier potential decreases. It will decrease . It will decrease approximately 2.5 mV for each <sup>0</sup>C increase.

# Field and capacitance of depletion layer

The two types of capacitances associated with a p-n junction diode are

1. Transition capacitance  $(C_T)$

2. Diffusion capacitance  $(C_D)$

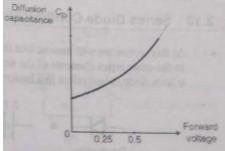

The transient capacitance C<sub>T</sub> referred to as space charge capacitance or barrier capacitance or depletion region capacitance. C<sub>T</sub> is not constant, depends on the magnitude of reverse voltage. The value of C<sub>T</sub> is inversely proportional to the width of depletion region and the width of depletion region is directly proportional the reverse voltage.

When the p-n junction diode is forward biased, a capacitance which is much larger then the transient capacitance is known as diffusion capacitance (C<sub>D</sub>) or storage capacitance.

The diffusion capacitance  $(C_D)$  is given by,

$$C_{\rm D} = \frac{dQ}{dV}$$

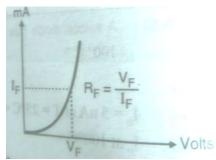

# Forward A.C. and D.C. resistance of junction

The two types of resistance associated with a p-n junction diode are

1. DC resistance

**2.** AC resistance

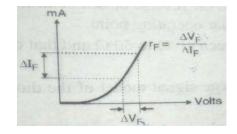

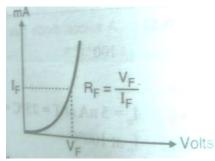

The resitance offered by the diode to the DC operating conditions is called as "DC resistance or Static resistance " denoted by R<sub>F</sub>. The DC resitance of a diode at operating point can be obtained by tacking the ratio of V<sub>F</sub> & C<sub>D</sub>

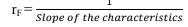

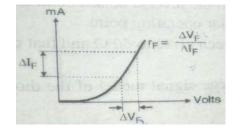

The resistance offered by the diode to the AC operating conditions is called as "AC resistance or Dynamic resistance" denoted by  $r_{\rm F}$ . AC resistance is actually the reciprocal of the slope of the forward characteristics

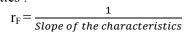

$$r_{\rm F} = \frac{1}{Slope \ of \ the \ characteristics}}$$

## **Reverse Breakdown**

The maximum reverse bais voltage that can be applied to a p-n diode is known as reverse breakdown voltage. The breakdown in a reverse biased diode can take place due to following effects :

1. Avalenche effect

# 2. Zener effect

Once the breakdown voltage is reached, a large number of the minority carrier suddenly appears in a depletion layer and the diode conducts heavily.

Due to large reverse voltage the velocity of the minority carrier will increase & hence kinetic energy associated with them will also increase. While travelling, these high kinetic energy carriers will collide with the stationary atoms and impart some kinetic energy to the valence electrons present in the covalent bonds. Due to additionally acquired energy, these valence electrons collide with further atoms bounded with covalent bonds, generating more free electrons.

The process continues in the geometric fashion, until the reverse current becomes huge. The breakdown voltage of a diode depends on how heavily doped the diode is. Normal diodes has breakdown usually greater than 50V.

The Zener breakdown occurs in high doping diodes, where as avalanche breakdown occurs at low doping diodes. The breakdown voltage in Zener is lesser then Avelanche breakdown voltage.

Doping

Breakdown voltage

Breakdown voltage Doping

The maximum reverse voltage that can be applied before entering the breakdown is called Peak inverse voltage (PIV) or Peak reverse voltage (PRV).

#### **Derivations**

- 1.  $\frac{\Delta V}{\Delta T}$  = -2.5mV/<sup>0</sup>C 2.  $\Delta V$  = (-2.5mV/<sup>0</sup>C) \*  $\Delta T$

- 3. %  $I_s = 100\%$  for a 10<sup>o</sup>C increase

- 4. %  $I_s = 7\%$  per <sup>0</sup>C

#### Long & Short Questions

Q.1. Explain what is meant by mobility of charge carrier in a solid. Derive an expression for the conductivity of semiconductor containing both electrons & holes in terms concentration and mobilities of charge carriers. [Kanpur 2010]

#### **Related Short Answer Questions**

- Define mobility of charge carriers in a semiconductor [Kanpur 1993,2000] (i)

- (ii) What do you mean by diffusion & diffusion current? [Kanpur 1995]

**Mobility**: This is a property of conductor defined as the ratio of drift velocity to applied electric field in a conductor denoted by  $\mu$ . Let us assume that when unit electric field is applied across the piece of metal causing drift velocity of v meter /sec, since drift velocity is directly proportional to electric field, we have

> $v \alpha E \implies v = \mu E$  $\therefore \qquad \mu = \frac{\nu}{E}$  $\therefore$  unit of  $\mu$  would be  $\frac{metere^2}{polt-sec}$

**Conductivity**: It is measure of the ease at which an current flows through the conductor. It is also defined as the inverse of resistivity denoted by  $\sigma$ :

$$\sigma = \frac{1}{\rho} \qquad (\rho = \text{resistivity})$$

$\therefore$  unit of  $\sigma$  is Siemens / meter

$J = \sigma E \implies \sigma = \frac{J}{E} = \frac{ne\mu}{E}$  (J= current density, n=no. of free electrons,

e=electronic charge, E= electric field)

Also

$$\therefore \ \sigma = \frac{J}{E} = \frac{1}{\rho}$$

In semiconductors, there are two types of charge carriers (electrons & holes) , therefore the conductivity of semiconductor due to conductivity of electrons( $\sigma_e$ ) & conductivity of holes( $\sigma_h$ ).

$$\sigma_e = \frac{J_e}{E} = \frac{nev_e}{E} = ne\mu_e$$

$$\sigma_h = \frac{J_h}{E} = \frac{pev_h}{E} = pe\mu_h$$

Total conductivity of a semiconductor

$\sigma = \sigma_e + \sigma_h = ne\mu_e + pe\mu_h$  (for intrinsic semiconductor  $n = p = n_i$ )

$\sigma_i = e n_i (\mu_e + \mu_h).$

Q.2. What are majority and minority charge carriers in n-type & p- type semiconductor ? Explain with diagram . What is doping ? [Kanpur 2005,12]

#### **Minority & Majority Carriers**

- In n-type semiconductor there is excessive free electrons so the majority carriers are electrons & holes are minority carriers where as in p-type semiconductor there is excess of holes therefore majority carriers are holes & electrons are minority carriers.

- For intrinsic semiconductor no. of electrons is same as the no. of holes, therefore, there is no minority & majority carriers

#### Doping

• Doping is the process of control addition of impurity in pure semi conductor, due to which conducting properties of semiconductor changes. The doped semiconductor is known as Extrinsic semiconductor.

• The impurities may be of two types

- Donor impurity( pentavalent atom) is used to manufacture n-type extrinsicsemiconductor.

- Acceptor impurity (trivalent atom) is used to manufacture p-type extrinsic- semiconductor.

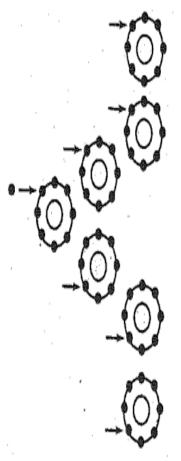

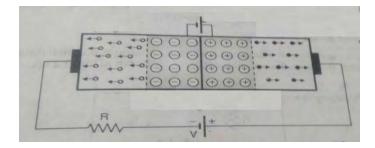

- We visualized the pentavalent atoms and free electrons n- type semiconductors as shown in fig.1. Each circled plus sign represents a pentavalent atom, and each minus sign is the free electron

- Similarly we visualized the trivalent atoms and free holes p- type semiconductors as shown in fig. Each circled plus sign represents a trivalent atom, and each plus sign is the hole.

| łu | e to        |       |            | _             |   |

|----|-------------|-------|------------|---------------|---|

|    | +0+0<br>0+0 | 0+0+0 | *O + O + O | +0 +0<br>0 +0 |   |

| ·  | φ           | ô.    | ô          | Θ             | ł |

Fig. 2 p-type semiconductors

| ē | ⊕ | ē | ⊕ |

|---|---|---|---|

| Ð | ē |   |   |

|   | ē | ⊡ | ⊕ |

Q.3. Derive expression for the densities of free electrons and holes in an instrinsic semiconductor. Show that the Fermi level lies half way between the conduction and valence bands. [Kanpur 92,94,97,98,2011,2013 important]

| <b>Related Short Answer Questions</b> |

|---------------------------------------|

|---------------------------------------|

(i) Define and explain 'Fermi Level' [Kanpur 2010]

- (ii) Define law of mass action

- In an intrinsic semiconductor, concentration of free electrons and holes is equal. Theoretical analysis reveals that under thermal equilibrium the product of concentration of free electrons and holes is constant. This is known as **law of mass action**.

$$ip = n_i^2$$

Where  $n_i$  is the intrinsic concentration and is the function of temperature. For an intrinsic semiconductor  $n = p = n_i$

# Fermi level

- Fermi level is simply a reference energy level. It is the energy level at which probability of finding electron n energy units above it in the conduction band is equal to probability of finding a hole n energy units below it in valence band.

- Let at any temp.  $T^0 K$ , no. of electrons in the conduction band be  $n_c$ , no. of electrons in the valence band be  $n_V$  and total no. of electrons in both band,  $n = n_c + n_V$

- No. of electrons in conduction band,  $n_C = nP(E_G)$ Where  $P(E_G)$  represents the probability of an electron having energy  $E_G$ . Its value may be determined from Fermi-Dirac probability distribution function given as

$$P(E) = \frac{1}{1 + e^{\frac{E_G - E_F}{KT}}}$$

P(E) is the probability of finding an electron having any particular value of energy E.

• The probability P(0) of an electron being found in the valence band with zero energy is

$$P(0) = \frac{1}{1 + e^{\frac{0 - E_F}{KT}}} = \frac{1}{1 + e^{\frac{-E_F}{KT}}}$$

So

Similarly

$$n_V = \frac{1}{1 + e^{\frac{-E_F}{KT}}}$$

$$n_C = \frac{n}{1 + e^{\frac{E_G - E_F}{KT}}}$$

Now, total no. of electrons in both the bands,

$$n = n_C + n_V = \frac{n}{1 + e^{\frac{E_G - E_F}{KT}}} + \frac{1}{1 + e^{\frac{-E_F}{KT}}}$$

{if n=1}

$$\implies \qquad 1 - \frac{1}{1 + e^{\frac{-E_F}{KT}}} = \frac{1}{1 + e^{\frac{E_G - E_F}{KT}}}$$

$$\implies \qquad E_F = \frac{1}{2}E_G$$

#### Q. 4. Describe diffusion of carriers in semiconductor.

- The movement of charge carriers from the region of high carrier concentration to the areas of low concentration, recombination of charge carriers occurs, the process is known as diffusion of carriers.

- The rate at which diffusion occurs depends on the velocity at which carriers move and on the distance between the carriers.

- This diffusion current is proportional to the concentration gradient :

$$J_{nd} = q.D_n.\frac{\partial n}{\partial x}$$

$$J_{pd} = -q.D_p.\frac{\partial p}{\partial x}$$

Where  $D_n$  and  $D_p$  are the diffusion constant of p and n- type semiconductor.

- Generally free electrons moves in conduction band & holes in valence band , valence band is more effected by electrostatic force so , we say mobility(it is the ease with which charge carriers flow) of electrons is higher then that of holes .

- The mobility of electron being higher than that of holes, the Einstein relationship shows that, for a given concentration gradient, the diffusion current for electrons is higher than the diffusion current for holes.

$$\frac{D_n}{\mu_n} = \frac{D_p}{\mu_p} = \frac{kT}{q}$$

## Q.5 What is p-n junction diode? How does a barrier field appear across a p-n junction ?

[Agra 2008,11]

|                                | Explain the pn junction at no bias |  |  |  |  |  |

|--------------------------------|------------------------------------|--|--|--|--|--|

| Related Short Answer Questions |                                    |  |  |  |  |  |

| (i)                            | Explain the term diode .           |  |  |  |  |  |

Or

#### **Junction Diode**

• The border b/w p-type and n-type semiconductor is called p-n junction, which has led to different inventions including diodes, transistors and integrated circuits.

| 0+ 0+ 0+ 0+<br>0+ 0+ 0 | + 0 + 0 +<br>+ 0 + | ē | ÷. ⊕i ⊕i ⊕ | ⊕ . ⊕ .<br>⊕ | ⊕ı ⊕ı ⊕i ⊕: |

|------------------------|--------------------|---|------------|--------------|-------------|

|------------------------|--------------------|---|------------|--------------|-------------|

- We visualized the pentavalent atoms and free electrons n- type semiconductors as shown on the right side of fig. . Each circled plus sign represents a pentavalent atom, and each minus sign is the free electron it contributes to the semiconductor.

- A manufacturer can produce a single crystal with p-type material on one side and n-type on the other side ,the region where these materials meet known as junction diode.

# **Barrier Potential**

- The free electrons on n side tend to diffuse across the junction, when free electrons enters the p region, it recombines with hole, and due to which hole disappears and free electron becomes valence electron.

- Each time an electron diffuses across a junction, it creates a pair of ions, +ve ion on n side and -ve ion on p side, these pair of ions at junction is called a dipole. As no. of dipoles builds up, empty charge region is created know as depletion region.

- Each dipole has electric field b/w the +ve & -ve ions. Therefore, if additional free electrons enters the depletion region, the electric field tries to push these electrons back into the n region. The electric field b/w the ions is equivalent to difference of potential called the barrier potential.

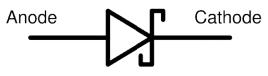

#### Diode

- The pn-junction itself forms the most basic semiconductor device called semiconductor diode. Thus semiconductor diode and pn junction are one and the same.

- The meaning of the term "diode" is the device having "two electrodes" (di-ode).

- As shown in fig., the diode has two electrodes one • each for the two regions on each side of the junction.

- The two electrodes named as anode and cathode • The current will flow through the diode, if and only if an external voltage source is connected to it with appropriate polarities.

- 0.6 Explain with suitable diagrams, why the energy levels of an atom becomes energy band in solids and hence explain the behavior of conductors, semiconductors and insulators.

#### or

What do you mean by energy band ? Distinguish clearly between a metal, semiconductors and insulator on the basis of energy bands in solids. [Kanpur 1994,97]

or

Why the energy levels of an atom become energy band in solids and hence explain the distinction between solid conductors, semiconductors and insulators. [Kanpur 1995, 2002]

Or

What do you mean by energy band in solids ? How are they formed ? How can you make a distinction between metal, insulators and semiconductor on the basis of these bands.

Electrode - Actrod

ΦŌ ē 0 Θ ΘΘΘ ē Ð ē ē φ ō õ Θ Ð ō ē ē

Creation of ions at junction

**Depletion layer**

| 0+ 0+ 0+ 0+<br>0+ 0+ 0+<br>0+ 0+ 0+ | -<br>-<br>-<br>- | . (⊕ i ⊕ i ⊕ i | ⊕ı ⊕ı ⊕ı ⊕ | ⊕ i ⊕ i ⊕ i ⊕ |

|-------------------------------------|------------------|----------------|------------|---------------|

|-------------------------------------|------------------|----------------|------------|---------------|

The pn junction

[Kanpur 1992]

Θ ó Θ Θ Ð Ð Ð Ō φφφ

Two types of semiconductors

# [Kanpur 1999]

[Kanpur 2009]

#### **Related Short Answer Questions**

(i) Distinguish metals, insulators and semiconductors [Kanpur 2004]

(ii) Explain conduction and valance band

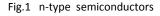

- In an isolated atom electrons are restricted to sets of discrete energy levels, with large gaps among them where no energy state is available for the electron to occupy.

- When these isolated atoms are brought together (interatomic spacing) to form a solid, various interactions (attraction and repulsion) occur between atoms, due to which same energy level has distinct value in different atom i.e. a same energy level has a band of energy.

- As interatomic spacing is decreased as shown in the fig., the energy band formed ,splits into two band separated by energy gap, known as forbidden gap.

- The higher energy band (upper band) is known as conduction band and the lower energy called valence band.

| Characteristics         | Insulator                                                   | Semiconductor                                   | Conductor                             |

|-------------------------|-------------------------------------------------------------|-------------------------------------------------|---------------------------------------|

| Conductivity            | Low                                                         | Moderate                                        | Vary High                             |

| Resistivity             | Vary High                                                   | Moderate                                        | Vary Low                              |

| Electrons availability  | small                                                       | moderate                                        | large                                 |

| Energy band<br>diagram  | Conduction<br>band<br>For bidden<br>band<br>Valence<br>band | Conduction<br>band<br>Energy<br>Valence<br>band | Conduction<br>band<br>Valence<br>band |

| Temperature coefficient | Negative                                                    | Negative                                        | Positive                              |

| Forbidden gap           | Large                                                       | Small                                           | No gap                                |

| Examples                | Paper, Mica, glass                                          | Silicon, Germinium                              | Matels, Aluminium,<br>Copper          |

#### Conductor, Semiconductor & Insulators

# Q.7. What is hall effect ? Obtain expression for hall coefficient and hall voltage and describe method for its determination. [Kanpur 2009]

#### **Related Short Answer Questions**

- (i) Define Hall co-efficient.

- (ii) Why is Hall Potential developed ?

Distance b/w atoms

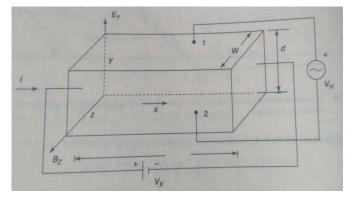

When a semiconductor sample carrying a current I is placed in a transverse magnetic field B, then an electric field  $E_0$  is induced in the specimen , in the direction perpendicular to both B and I, this phenomenon is called the **HALL effect**.

- Hall effect may be used for determining whether a semiconductor is *n*-type or *p*-type .If a current *I* is applied in the +ve x-direction and magnetic field in +ve z-direction, a force will be exerted in the –ve y-direction of the current carriers.

- The current is carried by electron from side 1 to side 2, if the semiconductor is *n*-type. Therefore Hall voltage appers between surfaces 1 & 2. The electric field developed in *y*-direction  $E_y$  is given by :

$$\frac{V_{\rm H}}{d} = E_{\rm y}$$

Where , d is the distance between surfaces 1 & 2 . In the equilibrium state the electric field  $E_y$  due to the Hall effect must exert force on the carrier, which just balances the magnetic force i.e.

$$eE_v = Bev_0$$

where e is magnitude of charge of carriers,  $v_0$  is the drift velocity. Current density J is given by :

$$J = \rho \mathbf{v}_0 = \frac{\mathbf{I}}{Wd}$$

Where ,  $\rho$  is the charge density & w is the width of the specimen in the direction of the magnetic field. Combing all the above relations, we have

$$V_H = E_v d = Bv_0 d = BJd/\rho = BI/\rho W$$

If the polarity of  $V_H$  is +ve at terminal 1 then the carrier must be an electron and  $\rho = n_0 e$  where  $n_0$  is the electron concentration. If the terminal 2 becomes positively charged w.r.t. terminal 1 the semiconductor must be of p-type and  $\rho = P_0 e$ , where  $P_0$  is the hole concentration:  $R_H = \frac{l}{\rho}$

Where  $R_H$  is the Hall coefficient.

$$R_H = \frac{V_H w}{BI}$$

Conductivity  $\sigma$  is related to p mobility  $\mu$  by :  $\sigma = n_0 e \mu$

$$\sigma = \rho_0 \mu \qquad \Longrightarrow \frac{1}{\rho_0} = \frac{\mu}{\sigma}$$

where,

$$\rho = n_0 e$$

If the conductivity is measured with Hall coefficient, mobility  $\mu$  can be determined by :

$$\begin{array}{ll} \because & J = \sigma E = \rho \mu E \\ \therefore & \frac{1}{\rho} = \frac{\mu}{\sigma} = R_H \\ \therefore & \mu = \sigma R_H \end{array}$$

In the presence of scattering the mobility can be approximately be written as :

$$\mu = \frac{8\sigma}{3\pi} R_H$$

#### Q.8 Explain work function in metals and semiconductor junction.

- Energy required for an electron to move from Fermi level into the free space known as work function.

- The schematic below in fig. a shows a metal and an *n*-type semiconductor. The dashed line at the top represents the zero of energy of free space.

- In fig. a, the work functions of metal & semi conductor denoted by  $\Phi_M \& \Phi_S$  resp.,  $E_F \& \mu$  indicates the fermi level of metal & semi conductor resp,  $\chi$  i.e. electron effinity.

- When contact is made as shown in fig. b, electrons lower their energy by flowing from the semiconductor conduction band into the metal.

- This continues until the fermi energy level in the semiconductor as shown in fig. c reaches equilibrium with the fermi energy of the metal.

- The deformed band structure shown in fig. d known as depletion layer forms a potential barrier.

# Q.9 Explain junction potential width of depletion layer.

- Width of depletion layer is the distance measured from one side to the other side of the depletion region.

- Due to the presence of depletion region the electrons and holes do not i.e. depletion region acts as a barrier.

- Due to the presence of immobile +ve (n-side) and -ve(p-side) ions on opposite sides of the junction an electric field is created across the junction. This electric field is known as junction potential.

- Also known as barrier potential, as it act as a barrier to oppose the flow of electrons and holes across the junction.

- Barrier potential is measured in volts. The barrier

potential for silicon is 0.7 volt whereas for germanium is 0.3 volt at  $25^{\circ}$ C.

• The built in potential  $V_{bi}$  at diode junction is

$$V_{bi} = \frac{\mathrm{KT}}{q} \ln\left(\frac{\mathrm{N}_{\mathrm{A}}\,\mathrm{N}_{\mathrm{D}}}{\mathrm{N}_{\mathrm{i}}^{2}}\right)$$

where  $N_A = Acceptor [], N_D = Donor [], N_i = instrinsic [], K= Boltzmann constant$

• The width d of depletion region is

$$d = \sqrt{\frac{2\xi_0}{q}} \left(\frac{1}{N_A} + \frac{1}{N_D}\right) V_{bi}$$

# Q.10 Draw & explain the characteristic curve of P-N Junction diode . [Kanpur 2014, important]

Or

# Explain the effect of temperature on the reverse saturation current in a junction diode. [Kanpur 2015, important]

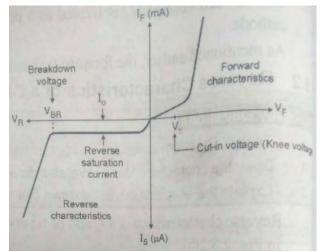

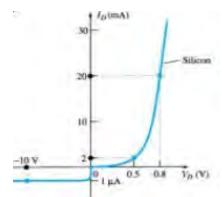

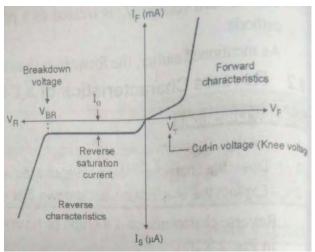

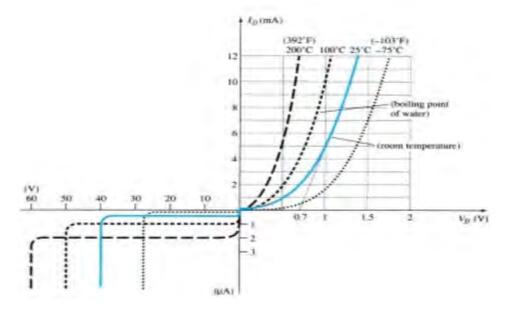

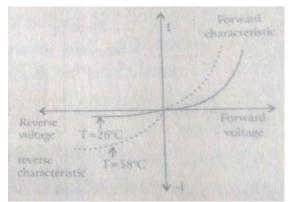

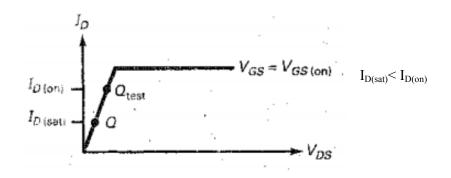

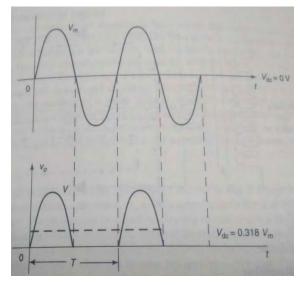

The V-I characteristics of p-n junction diode is a graph of voltage across the diode versus the current flowing through it . The V-I characteristics can be dived into two parts i.e. forward & reverse characteristics. The right side & left side of graph is forward & reverse characteristics respectively.

# Forward characteristics

- When the external voltage is applied on germanium (Ge)/silicon (Si)diode, is less then 0.3/0.7 volts, the Ge/Si diode allows negligible current to flow through it know as cut in voltage & the Cut off region of V-I characteristics.

- When the external voltage is applied on germanium (Ge)/silicon (Si)diode, is more above cut in voltage, current through the diode increases suddenly.

- The voltage at which the forward diode current increases rapidly is known as cut in voltage or Knee voltage. Knee voltage for Ge is 0.3V & for Si is 0.7V.

• The Forward characteristics of Si diode shifts to the left at a rate of 2.5mV per <sup>0</sup>C increase in temperature.

#### **Reverse characteristics**

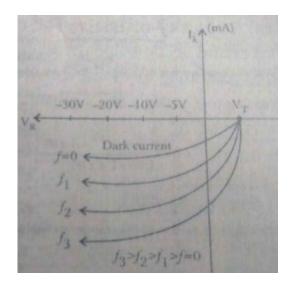

• Current flowing through a diode in the reverse biased state is known as reverse saturation current.

- As the reverse voltage is increased but below breakdown voltage( $V_{BR}$ ), the reverse saturation current remains constant, if the temperature is constant . However when the reverse voltage is above  $(V_{BR})$ , the large current flows

- The reverse saturation current in Si increases 100 % for each  $10^{\circ}$ C rise in temperature i.e. approximately equal to 7% for each  ${}^{0}C$  rise in temperature.

#### 0.11 Discuss the meaning of potential barrier &Junction capacitance of a P-N junction diode [Kanpur 2015] or

# Explain field and capacitance of depletion layer.

# **Barrier Potential**

- The free electrons on n side tend to diffuse across the junction, when free electrons enters the p region, it recombines with hole, and due to which hole disappears and free electron becomes valence electron.

- Each time an electron diffuses across a junction, it creates a pair of ions, +ve ion on n side and -ve ion on p side, these pair of ions at junction is called a dipole. As no. of dipoles builds up, empty charge region is created know as depletion region.

- Each dipole has electric field b/w the +ve & -ve ions. Therefore, if additional free electrons enters the depletion region, the electric field tries to push these electrons back into the n region. The electric field b/w the ions is equivalent to difference of potential called the barrier potential.

The two types of capacitances associated with a p-n junction diode are

- 1. Transition capacitance  $(C_T)$

- 2. Diffusion capacitance  $(C_D)$

- The transient capacitance  $C_T$  referred to as space charge capacitance or barrier • capacitance or depletion region capacitance.

- $C_{T}$  is not constant, depends on the magnitude of reverse voltage. •

- The value of  $C_T$  is inversely proportional to the width of depletion region and the width of depletion region is directly proportional the reverse voltage.

- When the p-n junction diode is forward biased, a capacitance which is much larger then • the transient capacitance is known as **diffusion capacitance** ( $C_D$ ) or storage capacitance.

- The diffusion capacitance  $(C_D)$  is given by,

$$C_D = \frac{dQ}{dV} = \frac{dI(V)}{dV}T_F$$

, where  $T_F = transist time$

#### Q.12

## Explain how you will determine the static & dynamic resistance of p-n junction.

Or Differentiate between static & dynamic resistance of a diode.

Or

# Discuss A.C. and D.C. resistance of junction

two types of resistance associated with a p-n junction diode are

| _                   |                     | _ |             |          |   |                    |  |

|---------------------|---------------------|---|-------------|----------|---|--------------------|--|

| +O +O +O<br>O+ O+ O | +O +O +O<br>O +O +O | + | 0<br>0<br>0 | ⊕ ⊕ ⊕, ⊕ | ē | ÷<br>⊕ : ⊕ i ⊕ i ⊕ |  |

|                     |                     |   |             |          | _ |                    |  |

Creation of ions at junction

**Depletion layer**

- - - -- ---

| 0+ 0+ 0+ 0+<br>0+ 0+ 0+ 0+<br>0+ 0+ 0+ | • | ÷ ⊕ i ⊕ i ⊕ | ⊕ i ⊕ i ⊕ i ⊕ |  |

|----------------------------------------|---|-------------|---------------|--|

|                                        |   |             |               |  |

# The pn junction

# 1. DC resistance

- **2.** AC resistance

- The resitance offered by the diode to the DC operating conditions is called as "DC resistance or Static resistance " denoted by R<sub>F</sub>

- The DC resitance of a diode at operating point can be obtained by tacking the ratio of  $V_F \& C_D$

- The resistance offered by the diode to the AC operating conditions is called as "AC resistance or Dynamic resistance" denoted by  $r_{\rm F}$ .

- AC resistance is actually the reciprocal of the slope of the forward characteristics .

Q.13. Discuss the different types of junction breakdown that can occur in a reverse biased diode. Or

# What do you mean by Zener & Avalanche breakdown in the barrier layer of a semiconductor ?

# Or

# Explain the two breakdown mechanisms of a reverse bias diode.

- The maximum reverse bais voltage that can be applied to a p-n diode is known as **reverse breakdown voltage**.

- The breakdown in a reverse biased diode can take place due to following effects :

- 1. Avalenche effect

- 2. Zener effect

- Once the breakdown voltage is reached, a large number of the minority carrier suddenly appears in a depletion layer and the diode conducts heavily.

- Due to large reverse voltage the velocity of the minority carrier will increase & hence kinetic energy associated with them will also increase.

- While travelling, these high kinetic energy carriers will collide with the stationary atoms and impart some kinetic energy to the valence electrons present in the covalent bonds.

- Due to additionally acquired energy, these valence electrons collide with further atoms bounded with covalent bonds, generating more free electrons.

- The process continues in the geometric fashion , until the reverse current becomes huge.

- The breakdown voltage of a diode depends on how heavily doped the diode is. Normal diodes has breakdown usually greater than 50V.

- The Zener breakdown occurs in high doping diodes, where as avalanche breakdown occurs at low doping diodes.

- The Zener breakdown voltage is lesser then Avelanche breakdown voltage.

Doping

Breakdown voltage

• If the breakdown occurs at -4v it is zener breakdown, but if the breakdown occurs above -6v it is avalanche breakdown, however if breakdown occurs between -4v to -6v, it may be avelance or zener breakdown.

# Q.14 Define mobility of charge carriers in a semiconductor. Derive expressions for their drift conduction and diffusion conduction. [Kanpur 1993,2000]

#### Or

# What do you mean by diffusion & diffusion current ? Find an expression for the total electron current and hole current in a semiconductor. [Kanpur 1995]

**Mobility :** This is a property of conductor defined as the ratio of drift velocity to applied electric field in a conductor denoted by  $\mu$ . Let us assume that when unit electric field is applied across the piece of metal causing drift velocity of v meter /sec, since drift velocity is directly proportional to electric field , we have

$$v \alpha E \implies v = \mu E$$

$\therefore \quad \mu = \frac{v}{E}$

$\therefore \text{ unit of } \mu \text{ would be } \frac{metere^2}{volt-sec}$

The Current flowing through the semiconductor due to diffusion of carriers is known as **diffusion Conduction**, the diffusion current density is directily proportional to concentration gradient

$$J_n \ \alpha \ \frac{dn}{dx} \implies J_n = qD_n \ \frac{dn}{dx}.$$

$$J_p \ \alpha \ \frac{dp}{dx} \implies J_n = -qD_p \ \frac{dp}{dx}.$$

Where  $D_n \& D_p$  are diffusion constants for n-type & p-type semiconductors

Einstein rel<sup>n</sup>

$$D_n \ \alpha \ \mu_n$$

$$D_p \ \alpha \ \mu_p$$

$$\frac{D_n}{D_p} = \frac{\mu_n}{\mu_p} = V_T = \frac{KT}{q}$$

Current flowing through the semiconductor under the applied E-field called Drift current

$$J_n = qn\mu_n E$$

$$J_p = qn\mu_p E$$

#### Numerical

Q.1 Find the conductivity ( $\sigma$ ) & resistivity ( $\rho$ ) of an instrinsic semiconductor at temp. of 300<sup>0</sup>K. It is given that n<sub>i</sub>=2.5 x 10<sup>13</sup>/cm<sup>3</sup>,  $\mu_n$ =3,800cm<sup>2</sup>/sV,  $\mu_p$ =1,800cm<sup>2</sup>/sV, q= 1.6 x10<sup>-19</sup> C.

Exp: As  $n_i=2.5 \times 10^{13}/cm^3$

$\mu_n$ =3,800cm<sup>2</sup>/sV,  $\mu_p$ =1,800cm<sup>2</sup>/sV , q= 1.6 x10<sup>-19</sup> C

: Conductivity of instrinsic semiconductor  $(\sigma_i) = n_i e(\mu_n + \mu_p)$

- ∴  $\sigma_i = 2.5 \times 10^{13} \times 1.6 \times 10^{-19} (3,800+1800) = 0.0224$  S/cm Ans

- ::  $\rho_i = 1/\sigma_i = 1/0.0224 = 44.64 \ \Omega$ -cm Ans

- Q.2. The instrinsic carrier concentration for silicon at room temperature  $(300^{0}$ K) is  $1.5x 10^{10}$ /cm<sup>3</sup>. If the mobility of electrons and holes are 1300cm<sup>2</sup>/sV & 450cm<sup>2</sup>/sV resp. what is the conductivity of silion at  $300^{0}$ K? If silicon is doped with  $10^{18}$  boron atoms /cm<sup>3</sup>, what is its conductivity?

Exp: Given  $n_i = 1.5 \times 10^{10} / \text{cm}^3$

$\mu_n = 1300 \text{ cm}^2/\text{sV},$

$\mu_p = 450 \text{ cm}^2/\text{sV}$

: Conductivity of instrinsic semiconductor  $(\sigma_i) = n_i e(\mu_n + \mu_p)$

$\therefore$   $\sigma_i = 1.5 \times 10^{10} \times 1.6 \times 10^{-19} (1300 + 450) = 4.2 \times 10^{-6}$

:

$$N_A = 10^{18} / cm^3$$

∴ Conductivity of a resulting P-type silicon semiconductor,  $\sigma_p = e N_A \mu_p = 1.6 \text{ x} 10^{-19} \text{ x} 10^{18} \text{ x} 450$

$$= 72$$

S/cm Ans

Q.3. If germanium is doped with  $2x \ 10^{21}$  atoms /m<sup>3</sup> atoms of aluminium then determine (i) Hole concentration (ii) concentration of free electrons (iii) conductivity at room temperature. Given  $\mu_n=0.17 \text{ m/sec/v/m}, E_g=0.7 \text{eV}$ . [Kanpur 1996,2003]

Exp: If we assume that all the acceptor atoms contributes to conduction then

Hole concentration =  $2 \times 10^{21}$  atoms /m<sup>3</sup>

The free electron density in intrinsic semiconductor

$$n_i = N_C e^{-(E_c - E_f)} / KT$$

, where  $N_C = 2(2\pi m_e kT/h^2)^{3/2}$

$$= 2^{*} \left(\frac{2^{*}3.14^{*}9.1x10^{-31}*1.38x10^{-23}}{6.6^{*}10^{-34}}\right)^{\frac{3}{2}} e^{\frac{-0.7^{*}1.6^{*}10^{-19}}{2^{*}1.38^{*}10^{-23}}}$$

$= 2.4 \times 10^{19} \text{ electron /cm}^3$

:. The no. of free electrons  $n = (n_i)^2 / p = (2.4 \times 10^{19})^2 / 2 \times 10^{21} = 2.8 \times 10^{17}$

Conductivity  $\sigma = ep \ \mu_n = 1.6 \ x 10^{-19} x \ 2x 10^{21} x 0.17 = 54.4 mhv.$

Q.4. In an N-type semiconductor, the Fermi level lies 0.5 eV below the conduction band. If the concentration of doner atoms is tripled, find the new position of the fermi level, taking the value kT=0.3eV. [Kanpur 2013]

Exp:  $E_C - E_F = 0.5 eV$  at a given conc<sup>n</sup> (let it be N<sub>D</sub>)

New conc<sup>n</sup>  $(N'_d) = 3 * N_D$

Let new fermi levl position be E'<sub>f</sub>

We know that  $n=n_d=N_e e^{\frac{E_f-E_c}{kT}}$

$$\frac{N'_d}{N_d} = \frac{e^{\frac{E'_f - E_c}{kT}}}{e^{\frac{E_f - E_c}{kT}}}$$

$$\implies 3 = \frac{\frac{0.5}{e^{KT}}}{\frac{E_f - E_c}{kT}} \quad \text{(taking } ln \text{ both sides)}$$

$$\implies \ln 3 = \frac{0.5 + (E_f - E_c)}{0.03} \text{ (kT=0.03eV)}$$

$$\implies E_c = E_c - 0.5 \text{eV. } \ln 3 \text{ Ans}$$

Q.5 A sample of intrinsic germanium at room temperature has a carrier concentration of 2.4 \*  $10^{19/}$ m<sup>3</sup>·It is doped with anitimony at a rate of one antimony atom /  $10^8$  atom of germanium atom. If the concentration of germanium atom is  $4*10^{28}$  atoms/m<sup>3</sup>, find the hole concentration and conductivity of the semiconductor. Mobility of electron  $\mu_n$ =0.35m<sup>2</sup>/V-sec. [Kanpur 2006]

Exp: Given  $n_i=2.4 * 10^{19}$ ,  $N^= 4*10^{28}$   $N_D/N = 1: 10^8$   $\therefore N_D = 4*10^{28}/10^8 = 4*10^{22}$  doners/m<sup>3</sup>  $n \sim N_D = 4*10^{22}$  electrons / m<sup>3</sup>  $\therefore p = n_i^2 / N_D = (4*10^{28})^2 / 4*10^{22} = 1.4 *10^{16}$  holes /m<sup>3</sup> Q.6. Calculate the conductivity & resistivity of a p-type Ge crystal which is mixed by acceptor atoms of concentration  $2*10^{17}$  atoms/ cm<sup>3</sup> & all acceptor atoms are active, given that  $\mu_{h}=1900$  cm<sup>2</sup>/volts-sec, e=1.6\*10<sup>-19</sup> coulomb [Kanpur 1999]

Exp: Given

$$n_h = 2*10^{17} \text{ atoms/ cm}^3 = 2*10^{23} \text{ atoms/m}^3$$

$\mu_h = 1900 \text{ cm}^2/\text{volts} = 0.19 \text{ m}^2/\text{volts}$

$\because \sigma_p = e n_h * \mu_h$

$\therefore \sigma_p = 1.6*10^{-19}*2*10^{23}*0.19 = 6080 \text{ mho /m}$

$\because \rho_p = 1/\sigma_p$

$\therefore \rho_p = 1/6080 \Omega \text{-m}$

Q.7. A silicon bar is doped with donor impurities  $N_D = 2.25 \times 10^{15}$  atoms / cm<sup>3</sup>. Given the intrinsic carrier concentration of silicon at T = 300 K is  $n_i = 1.5 \times 10^{10}$  cm<sup>-3</sup>. Assuming complete impurity ionization, find the equilibrium electron and hole concentrations . Exp: As per the given data

$$N_{D} = 2.25 \times 10^{15} \text{ Atom / cm}^{3}$$

$$n_{i} = 1.5 \times 10^{10} / \text{ cm}^{3}$$

Since complete ionization taken place,

$$n_{0} = N_{D} = 2.25 \times 10^{15} / \text{ cm}^{3}$$

$$\therefore P_{0} \cdot n_{0} = n_{i}^{2}$$

$$\therefore P_{0} = n_{i}^{2} / n_{0} = (1.5 \times 10^{10})^{2} / 2.25 \times 10^{15} = 1*10^{5} / \text{cm}^{3} \text{ Ans}$$

Q.8 Assume electronic charge  $q = 1.6 \times 10^{-19}$  C, kT/q = 25 mV and electron mobility  $\mu_n = 1000$  cm<sup>2</sup>/V-s. If the concentration gradient of electrons injected into a P-type silicon sample is  $1 \times 10^{21}$ /cm<sup>4</sup>, find the magnitude of electron diffusion current density (in A/cm<sup>2</sup>). Exp: Given  $q = 1.6 \times 10^{-19}$  C, kT/q = 25 mV,  $\mu_n = 1000$  cm<sup>2</sup>/V-s.

From Einstin relation,

$$\frac{D_n}{D_p} = \frac{\mu_n}{\mu_p} = V_T = \frac{\kappa T}{q}$$

$$\Rightarrow D_n = 25mV * 1000cm^2/v - s = 25cm^2/s$$

Diffusion current Density J = q  $D_n \frac{dn}{dx}$

=

$$1.6 \times 10^{-19} \times 25 \times 1 \times 10^{21}$$

= 4000 A / cm<sup>2</sup> Ans

- Q.9 When a silicon diode having a doping concentration of  $N_A = 9 \times 10^{16}$  cm<sup>-3</sup> on p-side and  $N_D = 1 \times 10^{16}$  cm<sup>-3</sup> on n-side is reverse biased, the total depletion width is found to be 3  $\mu$ m. Given that the permittivity of silicon is  $1.04 \times 10^{-12}$  F/cm, find the depletion width on the p-side and the maximum electric field in the depletion region.

- Exp: Given  $N_A = 9 \times 10^{16}$  / cm<sup>3</sup>;  $N_D = 1 \times 10^{16}$  / cm<sup>3</sup> Total depletion width,  $x = x_n + x_p = 3 \mu m$ .

$$\in = 1.04 \times 10^{-12} \text{ F / cm}$$

Since  $\frac{X_n}{X_p} = \frac{N_A}{N_D} = (9 \times 10^{16})/(1 \times 10^{16})$

$X_n = 9X_p$

$\therefore x = x_n + x_p = 3 \ \mu\text{m.}$

$9 \ x_p + x_p = 3 \ \mu\text{m.}$

$\therefore x_p = 0.3 \ \mu\text{m}$

Max. Electric field, E= qN\_AN\_D /  $\in = (1.6*10^{-19}*9 \times 10^{16}*1 \times 10^{16}) / (1.04 \times 10^{-12})$

$= 4.15 \times 10^5 \text{ V / cm Ans}$

- Q.10 A diode has a power rating of 5W. if the diode voltage is 1.2 V and the diode current is 17.5 A, what is the power dissipation ? will the diode be destroyed ?

- Exp:  $: P_D = V_D I_D$

$\therefore P_{D} = (1.2V)(1.75A) = 2.1W$

$:: P_D < 5W$  so the diode will not destroyed.

# Q.11. Find the dynamic resistance of a P-N junction diode at a forward current of 2mA. Assume kT/q= 25mV.

Exp: Given , forward current = 2mA = 0.002A

Volt equivalent of temp.,  $V_T = kT/q = 25mV$

: Dyamic resistance (r) =  $\eta V_T/I$  ( $\eta$ =1)

$\therefore$  r = 0.025/0.002= 12.5  $\Omega$ .

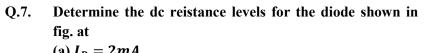

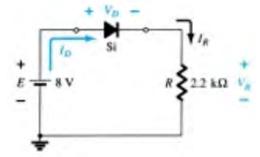

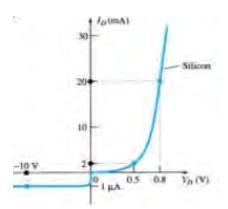

#### Q.12 Determine the dc reistance levels for the diode shown in fig. at

(a)  $I_D = 2mA$ (b)  $I_D = 20mA$ (c)  $V_D = -10V$ Exp: (a) At  $I_D = 2mA$ ,  $V_D = 0.5 v$ (from the curve)  $\therefore R_D = V_D / I_D = 0.5 v / 2mA = 250 \Omega$ (b) At  $I_D = 20mA$ ,  $V_D = 0.8 v$ (from the curve)  $\therefore R_D = V_D / I_D = 0.8 v / 20mA = 40 \Omega$ (c) At  $V_D = -10V$ ,  $I_D = -1\mu A$  (from the curve)  $\therefore R_D = V_D / I_D = -10v / -1\mu A = 10 M\Omega$

Q.13 Assuming the barrier potential of 0.7V at an ambient temperature of 25°C, What is the barrier potential of a silicon diode whwn the junction temperature is 100°C? At 0°C?

Exp: When the Junction temp. is  $100^{\circ}$ C, the change in barrier potential is  $\Delta V = (-2.5 \text{mV}/^{\circ}\text{C}) \Delta T = (-2.5 \text{mV}/^{\circ}\text{C})(100^{\circ}\text{C} - 25^{\circ}\text{C}) = -187.5 \text{mV}$   $\therefore$  The barrier potential will decrease by 187.5 mV i.e.  $V_{\text{B}} = 0.7 \text{V} - 0.18 \text{V} = 0.52 \text{ V}$  Ans When the Junction temp. is  $0^{0}$ C , the change in barrier potential is

$\Delta V = (-2.5 \text{mV}/^{0}\text{C}) \Delta T = (-2.5 \text{mV}/^{0}\text{C})(0^{0}\text{C} - 25^{0}\text{C}) = 62.5 \text{mV}$

$\therefore$  The barrier potential will increase by 62.5mV

i.e.  $V_B = 0.7V = 0.0625 = 0.7625 V$  Ans

# Q.14. A Silicon diode has a saturaration current of 5nA at $25^{\circ}C$ . What is the saturation current at $100^{\circ}C$ ?

Exp: The change in temp

...

$\therefore \Delta T = 100^{\circ}C - 25^{\circ}C = 75^{\circ}C$

$\div$  there is seven doubling between 25  $^{0}\mathrm{C}$  to 95  $^{0}\mathrm{C}$

$I_s = (2^7)(5nA) = 640nA$

- : there is 5  $^{\circ}$ C rise in temp from 95  $^{\circ}$ C to 100  $^{\circ}$ C

- :  $I_s = (1.07^5)(640 \text{ nA}) = 898 \text{ nA}$  Ans

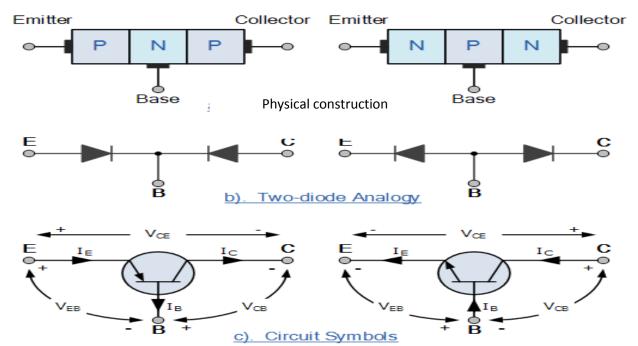

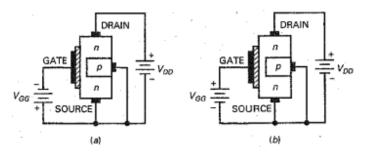

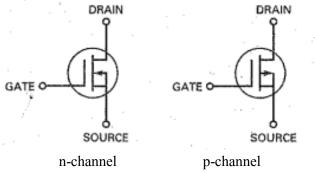

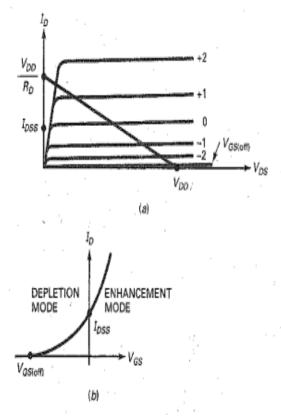

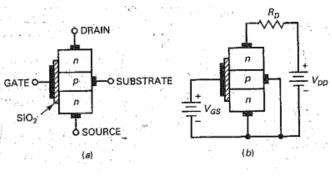

# <u>Chapter-2</u> <u>Semiconductor Devices</u>

#### pn Junction

It is a border between p-type & n-type semiconductor. The pn- junction itself forms the most basic semiconductor device called semiconductor diode, thus semiconductor diode and pn junction are one and the same.

#### **Depletion layer**

In pn junction diode the the free electrons on n side tend to diffuse across the junction ,when free electrons enters the p region, the free electrons recombines with hole in p region, and due to which hole disappears and free electron becomes valence electron.

Each time an electron diffuses across a junction, it creates a pair of ions, +ve ion on n side and -ve ion on p side, these pair of ions at junction is called a dipole. As no. of dipoles builds up, empty charge region is created know as depletion region.

## Junction Potential width of depletion layer

Width of depletion layer is the distance measured from one side to the other side of the depletion region. Due to the presence of depletion region the electrons and holes do not i.e. depletion region acts as a barrier. Due to the presence of immobile +ve(n-side) and -ve (p-side) ions on opposite sides of the junction an electric field is created across the junction. This electric field is known as junction potential also known as barrier potential. The barrier potential for silicon is 0.7 volt whereas for germanium is 0.3 volt at  $25^{\circ}$ C.

#### **The Energy Hill**

The barrier potential of a diode looks like an energy hill. Electrons attempting to cross the junction need to have enough energy to climb this hill. An external voltage source that forward-bias the diode gives electrons the energy required to pass through the depletion layer.

#### **Barrier Potential & Temperature**

When the junction temperature increases, the depletion layer becomes narrow & the barrier potential decreases. It will decrease approximately 2.5 mV for each <sup>0</sup>C increase.

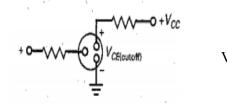

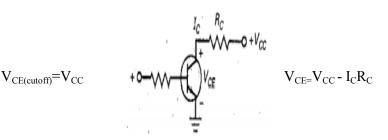

#### Forward bias & Reverse bias

When an external voltage opposes the junction potential, the diode is forward biased. If the applied voltage is greater than the barrier potential, the current flows. When an external voltage aids the barrier potential, the diode is reverse biased.

# Knee Voltage or Cut-in voltage

The voltage at which the forward diode current increases rapidly is known as Knee voltage or cut in voltage. Knee voltage for germanium is 0.3V & for silicon is 0.7V.

#### **Peak Inverse voltage**

The maximum reverse bais voltage that p-n diode can withstand without breaking down is known as peak inverse voltage.

## **Reverse saturation current**

Current flowing through a diode in the reverse biased state is known as reverse saturation current (I<sub>s</sub>). The reverse saturation current in Si increases 100 % for each  $10^{\circ}$ C rise in temperature i.e. approximately equal to 7 % for each  $^{\circ}$ C rise in temperature.

#### **Reverse Breakdown**

The reverse bais voltage above PIV leads to breakdown of voltage . The breakdown in a reverse biased diode can take place due to following effects :

- 1. Avalenche Breakdown

- 2. Zener Breakdown

Once the breakdown voltage is reached, a large number of the minority carrier suddenly appears in a depletion layer and the diode conducts heavily.

Due to large reverse voltage the velocity of the minority carrier will increase & hence kinetic energy associated with them will also increase. While travelling, these high kinetic energy carriers will collide

with the stationary atoms and impart some kinetic energy to the valence electrons present in the covalent bonds. Due to additionally acquired energy, these valence electrons collide with further atoms bounded with covalent bonds, generating more free electrons.

The process continues in the geometric fashion, until the reverse current becomes huge. The breakdown voltage of a diode depends on how heavily doped the diode is. Normal diodes has breakdown usually greater than 50V.

The Zener breakdown occurs in high doping diodes known as Zener diodes, where as avalanche breakdown occurs at low doping diodes known as Avelanche diodes . The breakdown voltage in Zener is lesser then Avelanche breakdown voltage.

## **Capacitance of depletion layer**

The accumulation of charge across the depletion region produces capacitance action, where depletion region acts as dielectric medium of the parallel plate capacitor(p-side and n-side as a plates of capacitor) Transition capacitance  $(C_T)$  & Diffusion capacitance  $(C_D)$  are two capacitances associated with a p-n junction diode.

#### **Resistance of pn Junction diode**

The two types of resistance associated with a p-n junction diode are

- 1. DC resistance

- **2.** AC resistance

The resitance offered by the diode to the DC operating conditions is called as "DC resistance or Static resistance " denoted by R<sub>F</sub>. The DC resitance of a diode at operating point can be obtained by tacking the ratio of V<sub>F</sub> & C<sub>D</sub>

The resistance offered by the diode to the AC operating conditions is called as "AC resistance or Dynamic resistance" denoted by  $r_{\rm F}$ . AC resistance is actually the reciprocal of the slope of the forward characteristics.

$$r_F = \frac{1}{Slope \ of \ the \ characteristics}$$

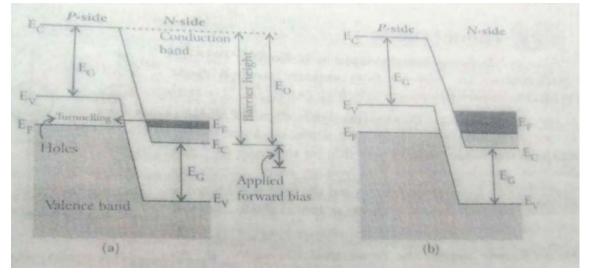

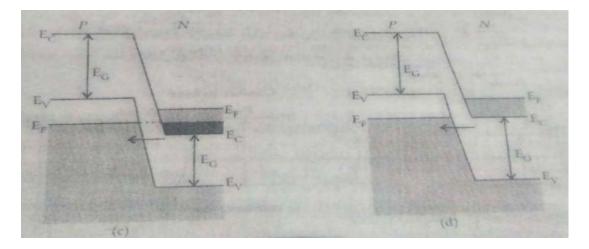

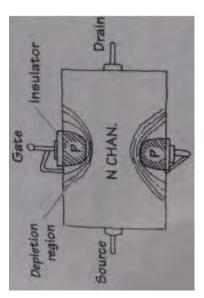

#### Tunnel diode

Such a diode having doping level  $\approx 10^{25}$ /m<sup>3</sup> in both P - N region of pn junction diode known as Tunnel diode. These diodes posses negative resistance & is useful for high-frequency circuits.

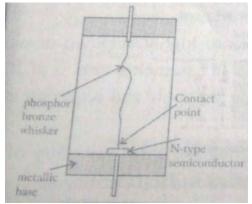

#### Point contact diode

It consists of a small wafer of a semiconducting crystal having an area of few square millimeter & a thickness of a fraction of mm. The crystal is soldered to a metallic base for external ohmic contact.

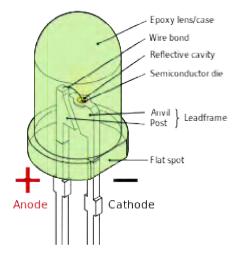

#### LED

Light emitting diode (LED) produces electromagnetic energy in the form of light widely used as an indicator on instruments, calculators and other electronic equipment. In ordinary diode energy is radiated in the form of heat but in an LED, the energy is radiated as light.

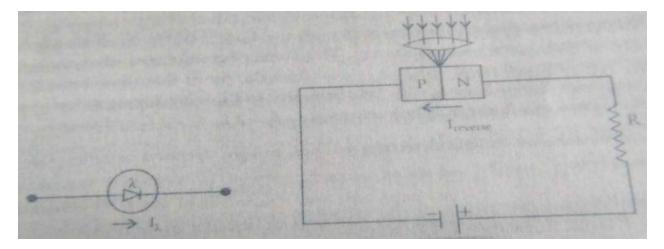

#### **Photodiodes**

Photodiode is a reverse biased P-N junction whose operation depends on the intensity of light. The incoming light produces free electrons and holes. The stronger the light, the greater the number minority carrier and the larger the reverse current.

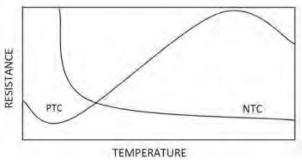

# Thermistors

A thermistor is a device which has negative temperature coefficient useful for making oscillator, amplifiers & switching devices.

## Derivations

- 1.  $\frac{\Delta V}{\Delta T}$  = -2.5mV/<sup>0</sup>C

- 2.  $\Delta V = (-2.5 \text{mV}/^{0}\text{C}) * \Delta T$

- 3. %  $I_s = 100\%$  for a 10<sup>o</sup>C increase

- 4. %  $I_{s} = 7\%$  per <sup>0</sup>C

# Long & Short Questions

Q.1. Explain the formation of depletion layer and barrier potential barrier in a p-n Junction diode. Find out the expression for the height of potential barrier and the width of depletion layer. [Important]

Or

Find out the expression for potential barrier and depletion width of a junction diode. [Kanpur 2016]

#### **Related Short Answer Question**

- (i) What is Junction diode? Explain the formation of depletion layer. [Kanpur 2013]

- (ii) What is a P-N Junction diode ? How does a barrier field appear across a P-N Junction?

[Kanpur 2011]

## Formation of depletion layer

- We visualized the pentavalent atoms and free electrons n- type semiconductors as shown on the right side of fig. . Each circled plus sign represents a pentavalent atom, and each minus sign is the free electron it contributes to the semiconductor .

- A manufacturer can produce a single crystal with p-type material on one side and n-type on the other side ,the region where these materials meet known as junction diode.

| $\begin{array}{c} \bigcirc + \bigcirc $ | $\begin{array}{c} \oplus i \ \oplus i \$ |

|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _                   |            |             |         | ·,       | 5                    |                             |                          |

|---------------------|------------|-------------|---------|----------|----------------------|-----------------------------|--------------------------|

| +O +O +O<br>O +O +O | 0+ 0+ 0+ 0 | + © + © + ⊙ | 0 0 0 0 | ⊕ ⊕ ⊕₊ ⊕ | i⊕<br>i⊕<br>i⊕<br>i⊕ | ÷<br>⊕<br>1 ⊕<br>1 ⊕<br>1 ⊕ | ē<br>⊕<br>i⊕<br>i⊕<br>i⊕ |

| 0+       0+       0+         0+       0+       0+         0+       0+       0+ |  | .⊕.⊕.<br>.⊕. |  | i⊕ i⊕ i⊕<br>⊙ |

|--------------------------------------------------------------------------------|--|--------------|--|---------------|

|--------------------------------------------------------------------------------|--|--------------|--|---------------|

Two types of semiconductors

Two types of semiconductors

Creation of ions at junction

- The free electrons on n side tend to diffuse across the junction, when free electrons enters the p region, it recombines with hole, and due to which hole disappears and free electron becomes valence electron.

- Each time an electron diffuses across a junction, it creates a pair of ions, +ve ion on n side and -ve ion on p side, these pair of ions at junction is called a dipole. As no. of dipoles builds up, empty charge region is created know as depletion region.

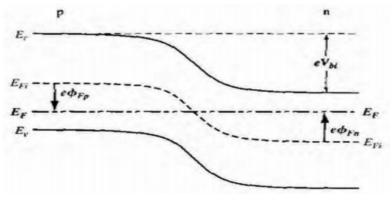

**Expression for barrier potential**

Energy Band diagram of a pn junction in thermal equilibrium.

The barrier potential maintains equilibrium, so no current is produced by this voltage. The intrinsic Fermi level is equidistant from the conduction band edge through the junction, thus the built-in potential barrier can be determined as the difference between the intrinsic Fermi level in the p and n regions.

i.e.  $V_{bi} = | \mathbf{\Phi}_{Fn} | + | \mathbf{\Phi}_{Fp} |$  (1) In the n region, the electron concentration in the conduction band is given by

$$n_0 = n_i \exp^{-(E_c - E_c)/KT}$$

(2)

Where  $n_i\& E_{Fi}$  are the intrinsic carrier concentration and instrinsic fermi energy resp. If  $\Phi_{Fn}$  is the potential in the n-region  $e \Phi_{Fn} = E_C - E_F$  (3)

Eq. (3) may be written as

$n_0 = n_i \exp^{-e \Phi_{Fn}} / KT$ (4)

Taking natural log both sides, setting  $n_0=N_D$

$$\ln(N_D/n_i) = -e\mathbf{\Phi}Fn/KT$$

(5)

$$\mathbf{\Phi}_{\mathrm{Fn}} = -\frac{KT}{q} * \ln(\mathrm{N_D}/\mathrm{n_i})$$

(6)

Similarly in p region, the concentration is given by  $P_0=N_A=n_iexp^{-(E_F-E_V)/KT}$  {since, e  $\Phi_{Fp}=1$

$$= N_{A} = n_{i} \exp^{-(E_{F} - E_{V})/KT} \qquad \{\text{since, e } \boldsymbol{\Phi}_{Fp} = E_{F} - E_{V} \}$$

(7)

$$\mathbf{\Phi}_{\mathrm{Fp}} = \frac{KT}{q} * \ln(\mathrm{N}_{\mathrm{A}}/\mathrm{n}_{\mathrm{i}}) \tag{8}$$

Substituting eq. (7) & (8) in eq. (1), we have

$$\mathbf{V}_{\mathrm{bi}} = \frac{KT}{q} * \ln(\frac{N_D N_A}{n_i^2}) = \frac{KT}{q} * \ln(\frac{N_D N_A}{n_i^2})$$

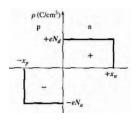

#### **Expression for depletion width**

Assuming that the space charge region abruptly ends in the n region at  $x = x_n$  and abruptly ends in the p region at  $x = x_p$ , we have

Potential in n region of diode is  $\Phi_n(x) = \frac{eN_D}{\epsilon} (x_n x - \frac{x^2}{2}) + \frac{eN_A}{2\epsilon_S} x_n^2 \qquad 0 \le x \le x_n$  (9)

Potential in p region of diode is  $\Phi_p(x) = \frac{eN_D}{\epsilon} (\frac{x^2}{2} + x_p x) + \frac{eN_A}{2\epsilon_s} x_p^2 \qquad -x_p \le x \le 0$  (10)

The magnitude of potential at  $x = x_n$  is equal to built in potential  $V_{bi}$

$$\mathbf{V}_{\mathbf{b}\mathbf{i}} = \frac{e}{2\epsilon} (N_D x_n^2 + N_A x_n^2) \tag{11}$$

$$\therefore \qquad x_n = \{\frac{2\epsilon V_{bi}}{\epsilon} [\frac{N_A}{N_D}] [\frac{1}{N_A + N_D}] \}^{\frac{1}{2}}$$

(12)

$$\therefore \qquad \frac{X_n}{X_p} = \frac{N_A}{N_D}$$

$$x_p = \left\{\frac{2\epsilon V_{bi}}{\epsilon} \left[\frac{N_D}{N_A}\right] \left[\frac{1}{N_A + N_D}\right]\right\}^{\frac{1}{2}}$$

(13)

Depletion or space charge width is  $W = x_n + x_p$ Using equation (12) & (13) we have

$$W = \left\{\frac{2\epsilon V_{bi}}{\epsilon} \left[\frac{N_A + N_D}{N_A N_D}\right]\right\}^{\frac{1}{2}}$$

(14)

Q.2. Describe the action of forward and reverse biased p-n junction semiconductor. Draw its V-I characteristics curve and explain it. [Kanpur 2014]

#### **Related Short Answer Question**

(i) Draw and explain the characteristics curve of a P-N Junction diode. [Kanpur 2014]

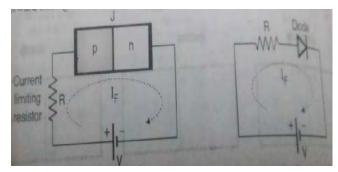

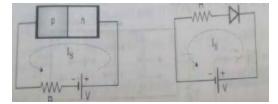

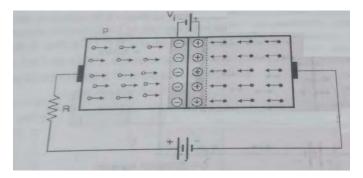

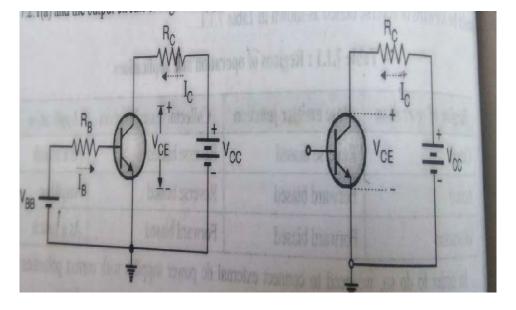

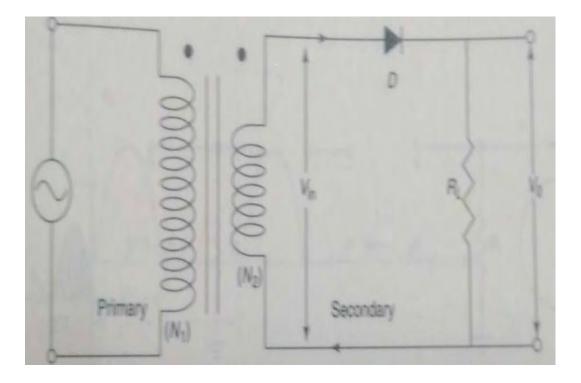

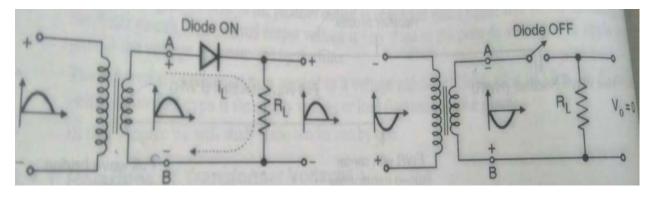

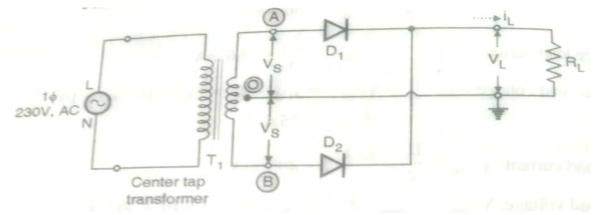

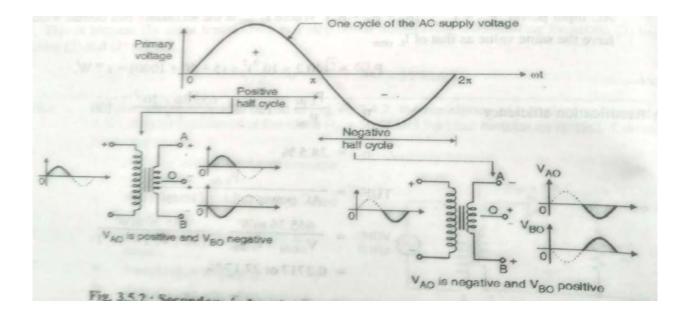

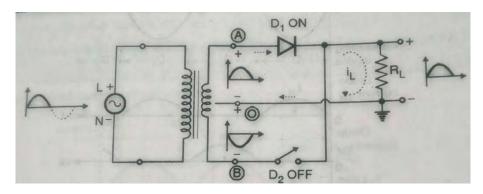

#### **Forward bias**

If the p- region(anode) of diode is connected to the +ve terminal of the external DC source and nregion (cathode) is connected to -ve terminal of the external DC source then the biasing is said to "forward biasing".

In forward bias width of depletion layer will reduce

#### **Reverse Bias**

If the p- region(anode) of diode is connected to the -ve terminal of the external DC source and n-

region (cathode) is connected to +ve terminal of the external DC source then the biasing is said to "reverse biasing".

In reverse bias width of depletion layer will increase.

#### V-I characteristics curve

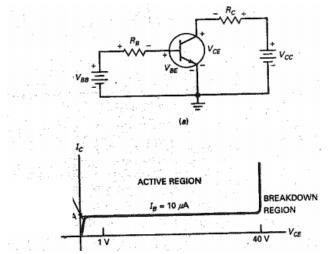

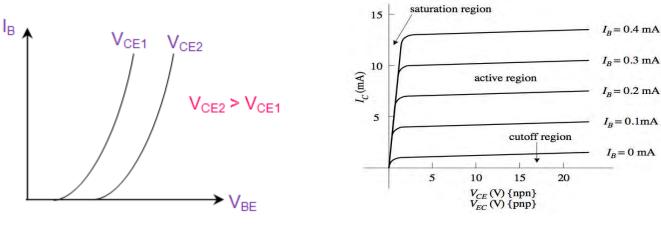

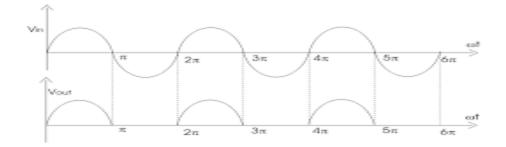

The V-I characteristics of p-n junction diode is a graph of voltage across the diode versus the current flowing through it . The V-I characteristics can be dived into two parts i.e. forward & reverse characteristics. The right side & left side of graph is forward & reverse characteristics respectively.

#### **Forward characteristics**

- When the external voltage is applied on germanium (Ge)/silicon (Si)diode, is less then 0.3/0.7 volts, the Ge/Si diode allows negligible current to flow through it know as cut in voltage & the Cut off region of V-I characteristics.

- When the external voltage is applied on germanium (Ge)/silicon (Si)diode, is more above cut in voltage, current through the diode increases suddenly.

- The voltage at which the forward diode current increases rapidly is known as cut in voltage or Knee voltage. Knee voltage for Ge is 0.3V & for Si is 0.7V.

- voltage for Ge is 0.3V & for Si is 0.7V. The Forward characteristics of Si diode shifts to the left at a rate of 2.5mV per <sup>0</sup>C increase in temperature.

#### **Reverse characteristics**

•

- Current flowing through a diode in the reverse biased state is known as reverse saturation current.

- As the reverse voltage is increased but below breakdown voltage( $V_{BR}$ ), the reverse saturation current remains constant, if the temperature is constant . However when the reverse voltage is above ( $V_{BR}$ ), the large current flows

- The reverse saturation current in Si increases 100 % for each 10<sup>o</sup>C rise in temperature i.e. approximately equal to 7 % for each <sup>o</sup>C rise in temperature.

Q.3. What is a junction diode ? What do you mean by biasing a junction diode ? Draw V-I characteristics curve of a junction diode under different biasing . [Important]

Or

What is junction diode ? Draw its characteristic junction curve.

[Kanpur 2016]

#### **Junction Diode**

The border b/w p-type and n-type semiconductor is called p-n junction, which has led to different inventions including diodes, transistors and integrated circuits.

#### Schematic of Junction diode

# Symbol of Junction diode

Reaming ref. to Q.2.

Q.4. Discuss the theory of current across p-n junction.

Or

#### Obtain the current-voltage equation for a p-n junction diode. [Important]

#### **Current across p-n junction**

The current in p-n junction flows due to majority & minority carriers present in p & n type semiconductor. The net current density through junction is due to following four contributions

- (a) The Current  $I_1$  due to flow of minority electrons from p-type to n-type.

- (b) The Current  $I_2$  due to flow of majority electrons from n-type to p-type.

- (c) The Current  $I_3$  due to flow of majority holes from p-type to n-type.

- (d) The Current  $I_4$  due to flow of minority holes from n-type to p-type.

Therefore  $I_{net} = (I_2 + I_3) - (I_1 + I_4)$

The current density for majority electrons from n-type

$$I_2 = \operatorname{Aexp}\left[\frac{-e(V_B - V)}{K_B T}\right]$$

Similary for holes

$I_3 = \text{Bexp}\left[\frac{-e(V_B - V)}{K_B T}\right]$

Hear A&B are constant,  $V_B$  is barrier and V is the applied voltage.

For no bias condition , no net current is flowing through the circuit , hence  $I_2=I_1$  and  $I_3=I_4$

$$\therefore \qquad I_1 = \operatorname{Aexp} \left[ \frac{-eV_B}{K_B T} \right]$$

$$\implies \qquad A = I_1 / \operatorname{Aexp} \left[ \frac{-eV_B}{K_B T} \right]$$

$$\therefore \qquad I_2 = I_1 \exp \left[ \frac{eV}{K_B T} \right]$$

Similarly

$$I_3 = I_4 \exp \left[ \frac{eV}{K_B T} \right]$$

$$\therefore \qquad I_{net} = (I_1 - I_4) \left[ \exp\left(\frac{eV}{K_B T}\right) - 1 \right] = I_0 \left[ \exp\left(\frac{eV}{K_B T}\right) - 1 \right]$$

This equation is known as **Schockley equation**,  $I_0$  is called reverse saturation current.

#### Q.5. Explain Junction resistance & Junction Capacitance in detail.

Or

Discuss the meaning of potential barrier and junction capacitance of a P-N junction diode

[Kanpur 2015]

#### **Related Short Answer Question**

(i) Define resistance of junction diode and obtain expression for them. [Kanpur 2016]

The two types of resistance associated with a p-n junction diode are

- 1. DC resistance

- **2.** AC resistance

- The resitance offered by the diode to the DC operating conditions is called as "DC resistance or Static resistance " denoted by  $R_F$

- The DC resitance of a diode at operating point can be obtained by tacking the ratio of  $V_F \& C_D$

- The resistance offered by the diode to the AC operating conditions is called as "AC resistance or Dynamic resistance" denoted by r<sub>F</sub>.

- AC resistance is actually the reciprocal of the slope of the forward characteristics .

The two types of capacitances associated with a p-n junction diode are

- 1. Transition capacitance  $(C_T)$

- 2. Diffusion capacitance  $(C_D)$

- The **transient capacitance** C<sub>T</sub> referred to as space charge capacitance or barrier capacitance or depletion region capacitance.

- $C_T$  is not constant, depends on the magnitude of reverse voltage.

- The value of C<sub>T</sub> is inversely proportional to the width of depletion region and the width of depletion region is directly proportional the reverse voltage.

- When the p-n junction diode is forward biased, a capacitance which is much larger then the transient capacitance is known as **diffusion capacitance** (C<sub>D</sub>) or storage capacitance.

- The diffusion capacitance  $(C_D)$  is given by,

$$C_D = \frac{dQ}{dV} = \frac{dI(V)}{dV}T_F$$

, where  $T_F = transist time$

Q.6. How current flow through pn junction ? Discuss effect of biasing on the width of depletion layer

#### **Related Short Answer Question**

(i) Draw the energy level diagram with Fermi level for an unbiased, forward biased and reverse biased pn junction. Explain the effect of biasing on the width of depletion layer. [Important ]

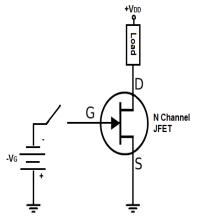

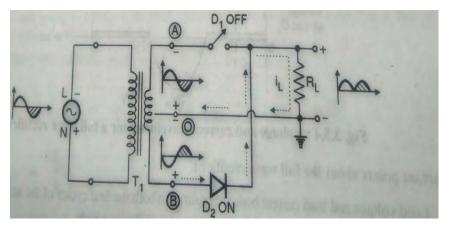

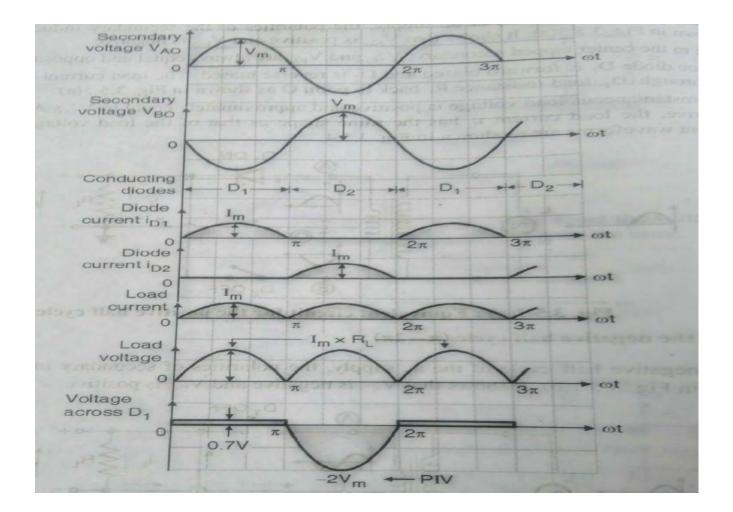

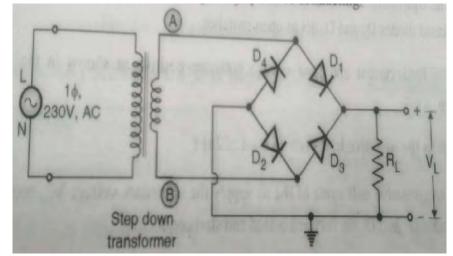

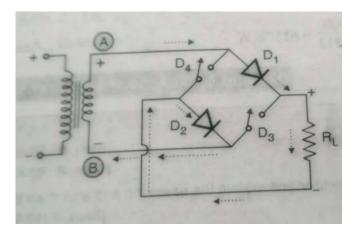

# Mechanism of current flow (Forward bias)

- When diode is forward bias, due to -ve terminal of external source connected to n-region, free electrons from n-side are pushed towards the p-side. Similarly the +ve end of supply will push holes from the p-side towards the n-side.

- With increase in the external supply voltage V, more and more number of holes (p-side) and electrons (n-side) start travelling towards the junction .

- The holes will start converting the negative ions into neutral atoms and the electrons will convert the positive ions into neutral atoms. As a result of this, the width of depletion region will reduce.

- Due to reduction of the depletion region width, the barrier potential will also reduce. Eventually at a particular value of V, the depletion region will collapse. There is absolutely no opposition to the flow of electron and holes.

- The large no. of majority carriers crossing the junction constitute a current called as the forward current.

- The forward current through a p-n junction diode flows due to the majority carriers and its direction of flow(conventional) is always from anode to cathode.

- There is a potential drop across the conducting forward biased diode denoted by  $V_F$  equal to 0.7V for silicon & 0.3V for germanium diode.

- The forward voltage drop is due to barrier potential & internal resistance.

# Mechanism of current flow (Forward bias)

- When the diode is reverse biased , holes in the p- region are attracted towards the negative terminal of the supply and electrons on the n- side are attracted towards the +ve terminal of the supply.

- Widening of depletion region : Due to movement of majority carriers away from the junction , width of depletion layer increases .

- The minority electrons on p-side are attracted by +ve end of dc supply. Hence these electrons will cross the junction and constitute the reverse current  $I_s$  of the diode.

- The reverse current flows due to minority carriers is also called as the "Reverse Saturation current", doubles its value for every 10°C rise in temperature.

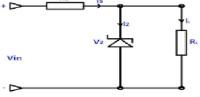

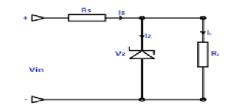

# Q.7. What are Zener diodes ? Explain its operation & characteristics. How a Zener diode can be used as a Voltage regulator ? [Important ]

## **Related Short Answer Question**

- (i) What is zener diode ? Plot & explain its characteristics curve. [Kanpur 2013]

- (ii) What is Zener diode ? How is Zener diode used as a voltage regulator in a power supply ? Explain. [Important]

- (iii) What is a breakdoen diode (Zener diode). Discuss the origin of breakdown of a junction. [Important]

## Zener Diode

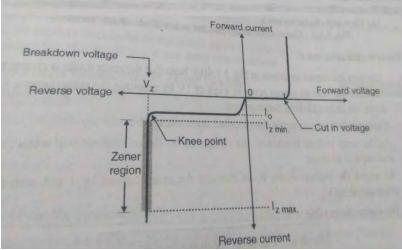

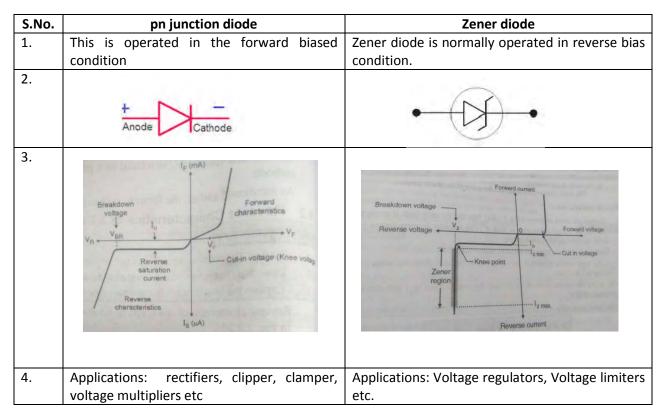

Zener diode is a special type of p-n junction semiconductor diode that are designed to operate in the breakdown region

The V-I characteristics of Zener diode is a graph of voltage across the diode versus the current flowing through it .This characteristic is divided into two parts

1. Forward Characteristics2.Reverse Characteristics

## **Forward Characteristics**

The Forward Characteristics of Zener diode is almost identical to forwar Characteristics of a p-n junction diode.

# **Reverse Characteristics**

- The Reverse Characteristics of Zener diode is substantially different from that of the p-n junction diode.

- As we increase the reverse voltage , initially a small reverse saturation current "I<sub>0</sub>" flows. This current flows due to thermally generated minority carriers.

- At a certain value of reverse voltage, the reverse current will increase suddenly and sharply. This is an indication that breakdown has occurred This breakdown is called as zener breakdown voltage or zener voltage denoted by V<sub>z</sub>.

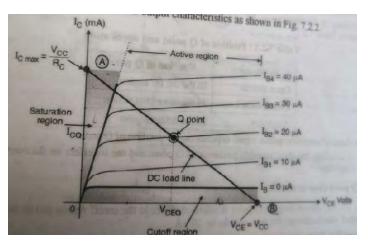

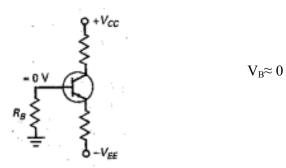

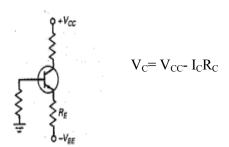

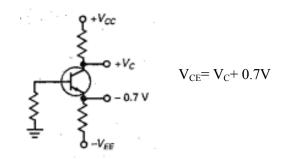

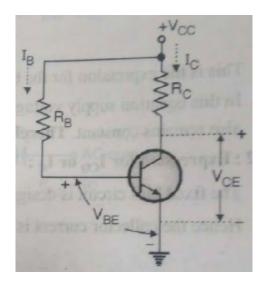

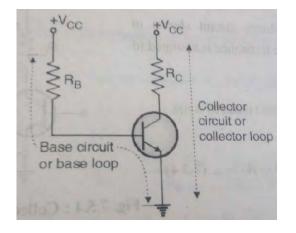

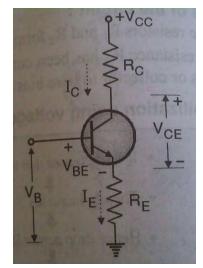

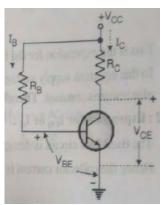

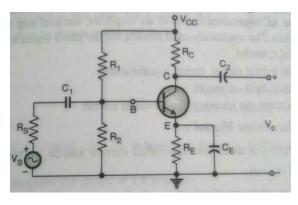

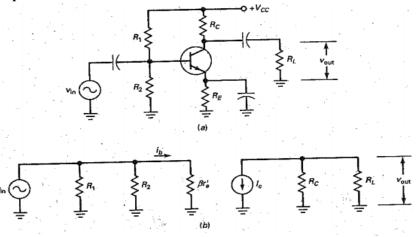

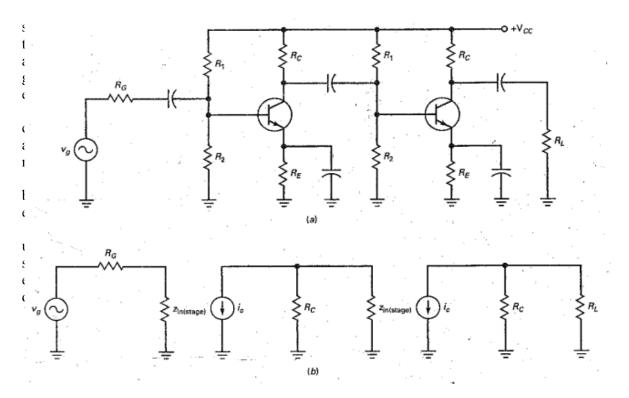

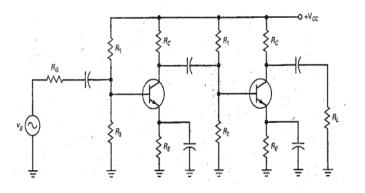

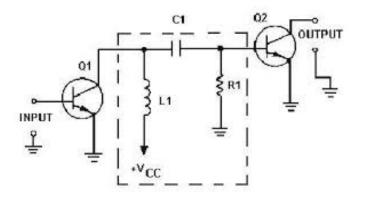

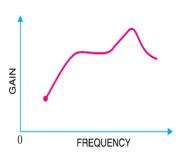

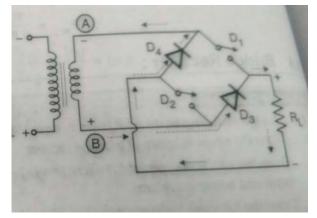

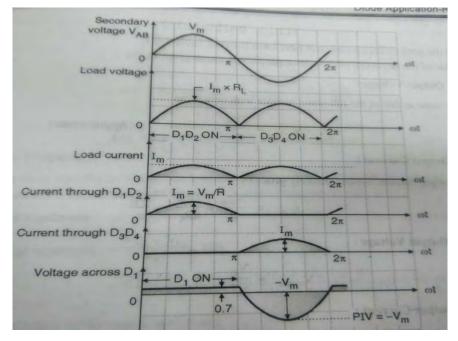

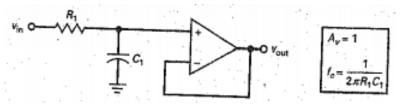

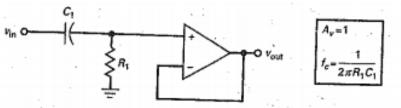

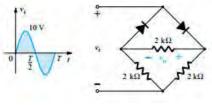

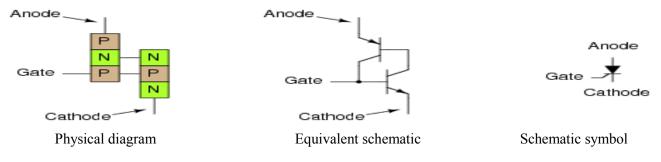

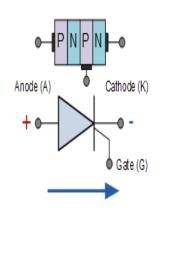

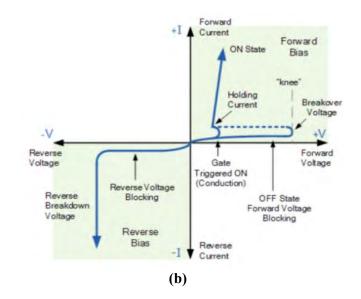

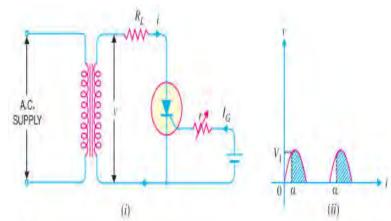

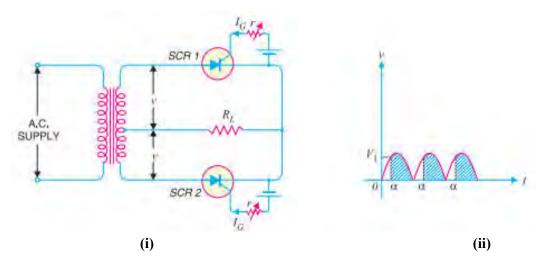

- After breakdown, the voltage across the zener diode remains constant equal to Vz