## **Transistor Biasing and Stabilization**

By

### Mr. Aniket Kumar

Assistant Professor, Department of Electronics & Communication Engineering Shobhit Institute of Engineering & Technology (Deemed to-be University) NH-58, Modipuram, Meerut – 250 110, India

#### Chapter-4 Transistor Biasing and Stabilization

#### Biasing

We known that transistor can operate in **a**ny of three regions of operation namely cutoff, active region and saturation. To operate the transistor in these regions the two junction of a transistor should be forward or reversed biased as shown in table

| <b>Region of operation</b> | <b>Base Emitter Junction</b> | Collector base junction | Application |

|----------------------------|------------------------------|-------------------------|-------------|

| Cut off                    | Reversed bias                | Reversed bias           | As a switch |

| Active                     | Forward bias                 | Reversed bias           | Amplifier   |

| Saturation                 | Forward bias                 | Forward bias            | As a switch |

In order to do so, we need to connect external DC power supplies with correct polarities & magnitude. This process is called as biasing of transistor.

#### Voltage divider bias (VDB)

The most famous circuit based on the emitter-bias prototype is called voltage divider bias. You can recognize it by the voltage divider in the base circuit.

#### **Accurate VDB Analysis**

The Key idea is for the base current to be much smaller than the current through the voltage divider. When the condition is satisfied, the voltage divider holds the base voltage almost constant and equal to the unloaded voltage out of the voltage divider. This Produces a solid Q point under all operating conditions

#### VDB load line & Q point

The load line is drawn through saturation and cut off. The Q point lies on the load line with the exact location determined by the biasing. Large variations in current gain have almost no effect on the Q point because this type of bias sets up a constant value of emitter current.

#### Two –Supply emitter bias

This design uses two power supplies: one positive and the other negative . The idea to set up a constant value of "emitter current".

#### Other types of bias

This section introduced negative feedback, a phenomenon that exits when an increase in an output quantity , produces decreases in an input quantity. It is brillent idea that led to voltage-divider bias. The other type of bias cannot use enough –ve feedback, so they fail to attain the performance level to voltage-divider bias.

#### **PNP Transistors**

These pnp devices have all current & voltages reversed from their npn counterparts. They may be used with negative power supplies; more commonly, they are used with +ve power supplies in an upside-down configuration.

#### **Reverse Feedback ratio**

If some percentage of an amplifier's output signal is connected to the input, so that the amplifier amplifies part of its own output signal, we have what is known as feedback. Feedback comes in two varieties: positive (also called regenerative), and negative (also called degenerative). Positive feedback reinforces the direction of an amplifier's output voltage change, while negative feedback does just the opposite.

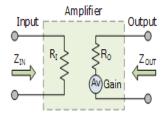

#### Input & Output impedances

It is the input impedance "seen" by the source driving the input of the amplifier.  $Z_{in}$  or Input Resistance is an important parameter in the design of a transistor amplifier and as such allows amplifiers to be characterized according to their effective input and output impedances as well as their power and current ratings.

For details refer to chapter 3

#### **Bias Stabilization**

The stability of a system is a measure of the sensitivity of a network to variations in its parameter. B increases with increase in temperature . Magnitude of  $V_{BE}$  decreases about 7.5 mV per degree Celsius (°C) increase in temperature. I<sub>CO</sub>(reverse saturation current): doubles in value for every 10°C increase in Temperature

#### Stability Factors, $S(I_{CO})$ , $S(V_{BE})$ , and $S(\beta)$

A stability factor, S, is defined for each of the parameters affecting bias stability as listed below:

$$\begin{split} S(I_{CO}) &= \Delta I_C / \Delta I_{CO} \\ S(V_{BE}) &= \Delta I_C / \Delta V_{BE} \\ S(\beta) &= \Delta I_C / \Delta \beta \end{split}$$

In each case, the delta symbol signifies change in that quantity.

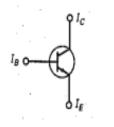

#### **BJT Transistor modeling**

A model is the combination of circuit elements , properly chosen, the best approximates the actual behavior of a semiconductor device under specific operating conditions.

The ac equivalent of a network is

- 1. Setting all dc sources to zero and replacing them by a short- circuit equivalent

- 2. Replacing all capacitors by a short-circuit equivalent.

- 3. Removing all elements bypassed by the short-circuit equivalents introduced by steps 1 & 2.

- 4. Redrawing the network in a more convenient and logical form.

#### **Transistor Model**

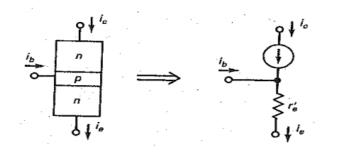

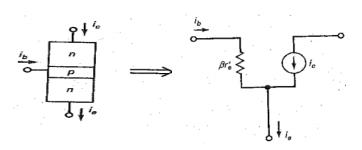

The T- Model (Ebers- Moll model)

| Туре                         | Circuit          | Calculations                                                                                                                        | Characteristics                                                              | Where used                           |

|------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------|

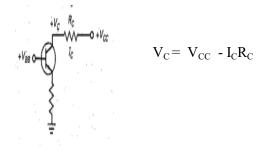

| Base bias                    |                  | $I_{B} = (V_{BB} - 0.7V)/R_{B}$ $I_{C} = \beta I_{B}$ $V_{CE} = V_{CC} - I_{C}R_{C}$                                                | Few parts; β<br>dependent;<br>fixed base<br>current                          | Switch; digital                      |

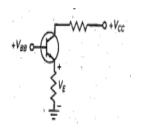

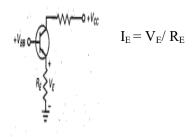

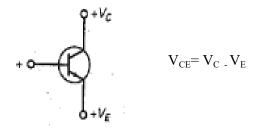

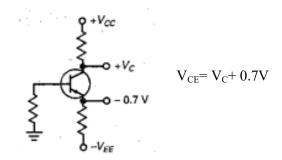

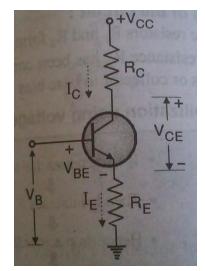

| Emitter bias                 | +V <sub>88</sub> | $V_{E} = V_{BB} - 0.7V$ $I_{E} = V_{E} / R_{E}$ $V_{C} = V_{C} - I_{C}R_{C}$ $V_{CE} = V_{C} - V_{E}$                               | Fixed emitter<br>current; β<br>independent                                   | I <sub>C</sub> driver ;<br>amplifier |

| Voltage divider<br>bias      |                  | $V_{B} =$ $R_{2}V_{CC}/(R_{1}+R_{2})$ $V_{E} = V_{B}-0.7V$ $I_{E} = V_{E}/R_{E}$ $V_{C} = V_{CC}-I_{C}R_{C}$ $V_{CE} = V_{C}-V_{E}$ | Needs more<br>resistors; β<br>independent;<br>needs only one<br>power supply | Amplifier                            |

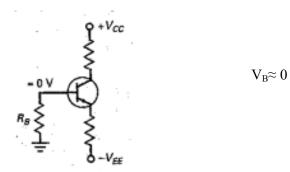

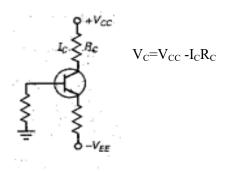

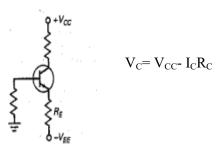

| Two – supply<br>emitter bias |                  | $V_{B=} 0V$ $V_{E}=V_{B}-0.7V$ $V_{RE}=V_{EE}-0.7V$ $I_{E}=V_{RE}/R_{E}$ $V_{C}=V_{CC}-I_{C}R_{C}$ $V_{CE}=V_{C}-V_{E}$             | Needs positive<br>& negative<br>power supplies;<br>β independent;            | Amplifier                            |

#### **VDB** Derivations

#### **Base voltage**

# $V_{BB} = R_2 V_{CC} / (R_1 + R_2)$ $R_1 + V_{BB}$ $R_2 + V_{BB}$

#### Emitter voltage

$V_E = V_{BB} - V_{BE}$

#### **Emitter current**

Collector voltage

#### TSEB (Two supply emitter bias) Derivations

#### **Base voltage**

#### **Collector Voltage (TSEB)**

**Collector current**

Collector – emitter voltage

$I_C\approx I_E$

**Emitter current**

#### **Collector-emitter Voltage (TSEB)**

#### Long & Short Questions

#### Q.1. What is meant by transistor –biasing ? Define Stability factor.

Or

#### What do you understand by transistor by transistor biasing ? Why it is necessary ?

**Transistor Biasing** is the process of setting a transistors DC operating voltage or current conditions to the correct level so that any AC input signal can be amplified correctly by the transistor.

#### Necessary of transistor biasing

- To active an transistor, biasing is essential. For proper working it is essential to apply to apply voltages of correct polarity across its two junctions.

- If it is not biased correctly it would work inefficiently and produce distortion in the output signal

- > Q-point is not middle Output signal is distorted & the signal is clipped

- > Further for various applications, BJT is biased as shown in table

| <b>Region of operation</b> | <b>Base Emitter Junction</b> | Collector base junction | Application |

|----------------------------|------------------------------|-------------------------|-------------|

| Cut off n                  | Reversed bias                | Reversed bias           | As a switch |

| Active                     | Forward bias                 | Reversed bias           | Amplifier   |

| Saturation                 | Forward bias                 | Forward bias            | As a switch |

| 0                          | ·                            | ·                       | •           |

In order to have these applications , we need to connect external DC power supplies with correct polarities & magnitude. This process is called as biasing of transistor.

#### **Stability Factor**

The stability of Q point of transistor amplifier depends on the following three parameters :

1. Leakage current  $I_{CO}$  2.  $\beta_{dc}$  3. Base to emitter voltage

The effect of these parameters can be expressed mathematically by defining the stability factors 1. Stability factor  $S = \frac{\Delta I_C}{C}$

Stability factor

$$S = \frac{C}{\Delta I_{CO}}$$

Constant  $V_{BE} \& \beta_{dc}$

This represents the change in collector current due to change in reverse saturation current  $I_{CO}$  The other two parameters that means  $V_{BE}$  &  $\beta_{dc}$  are assumed to be constant.

2. Stability factor

$$S'' = \frac{\Delta I_C}{\Delta V_{BE}}$$

Constant  $I_{CO} \& \beta_{dc}$

S" represents the change in  $I_C$  due to change in  $V_{BE}$  at constant  $I_{CO}\,\&\,\beta_{dc}$

3. Stability factor

$$S'' = \frac{\Delta I_C}{\beta dc} \Big|_{Constant I_{CO} \& V_{BE}}$$

Total change in collector current

$\Delta I_C = S. \Delta I_{CO} + S". \Delta V_{BE} + S". \beta dc$

- Ideally the values of all the stability factors should be zero and practically they should be as small as possible.

- Practically the value of S is significantly higher than the other two stability factor. Hence while comparing the biasing circuits, the values of S is more significant.

## Q.2. What are the various methods used for transistor biasing? Explain one method & State its advantage & disadvantages.

#### **Related Short Answer Questions**

(i) What do you mean by biasing of a transistor ? Explain with examples

Biasing is a technique to aid  $V_{BB}$  in the input circuit which is separate from the  $V_{CC}$  used in the output circuit. The following are the most commonly used method for transistor biasing are as below :

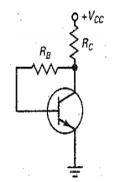

- 1. Fixed bias circuit (Single base resistor biasing) or base bias

- 2. Collector to base bias circuit

- 3. Voltage divider bias circuit (VDB) or self bias

- 4. Emitter bias or modified fixed bias circuit

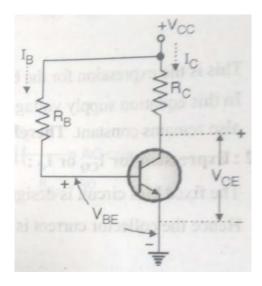

#### Fixed bias circuit (Single base resistor biasing) or base bias

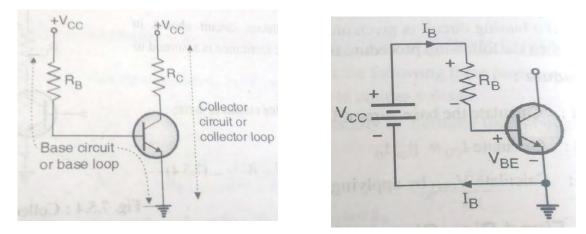

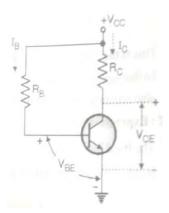

The simplest of all biasing is fixed bias ckt. as shown in fig.

- Before biasing we were using two separate power supplies i.e.  $V_{CC}$  &  $V_{BB}$  to bias a transistor.

- But in this circuit only one power supply has been used to supply power to both collector as well as base.

- $R_B$  is the single base biasing resistor , hence this circuit is also called as single base resistor biasing-

#### Analysis of Fixed bias circuit :

As shown in fig. splitting input & output terminals in two loops, namely base circuit & collector circuit

Fig. (a)

as shown in fig.(a).

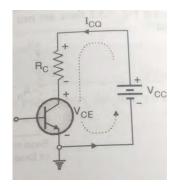

#### **Expression for I**<sub>B</sub>

- Consider the base circuit as shown in fig.(b) . Applying KVL to the base circuit we have  $V_{CC}\,+\,I_BR_B+V_{BE}\,{=}\,0$

- Rearranging the equation we get  $I_B = (V_{CC} V_{BE})/R_B$

- For silicon  $V_{BE} = 0.7$  and for germanium  $V_{BE} = 0.3V$

#### Expression for I<sub>C</sub> & V<sub>CE</sub>

Since the fixed bias is operated in the active region therefore

$$\begin{split} I_{C} &= \beta \ I_{B} + I_{CEO} \\ &: \beta \ I_{B} >>> I_{CEO} \\ &: I_{C} &= \beta \ I_{B} \end{split}$$

Applying KVL to the collector circuit shown, we have

$$\mathbf{V}_{\mathrm{CC}} - \mathbf{I}_{\mathrm{C}} \mathbf{R}_{\mathrm{C}} - \mathbf{V}_{\mathrm{CE}} = \mathbf{0}$$

$$\therefore V_{CE} = V_{CC} - I_C R_C$$

#### Advantages

- 1. The fixed bias circuit is simple and less number of components.

- 2. It give very good flexibility as the Q point can be set at any point in the active region by just adjusting the value of  $R_B$ .

#### Disadvantages

- 1. Vary poor thermal stability as  $S = 1 + \beta_{dc}$ .

- 2. With changes in  $\beta_{dc}$  due to change in temp., the operating point keeps on shifting its position.

- Q.3. What do you understand by 'Bias stability' of a transistor ? Why is it necessary ? Explain the working of self-bias circuit for common emitter BJT.

#### Or

Draw the circuit diagram of voltage diagram of voltage divider bias of a transistor . Explain its working.

For definition ref. Q.1

#### Self Bias

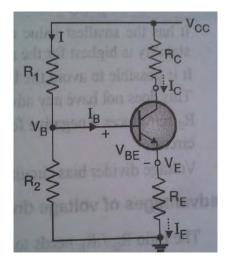

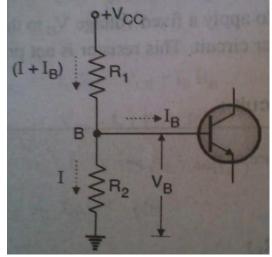

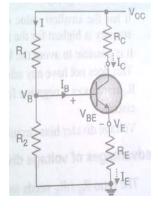

The voltage –divider biasing is known as self bias circuit. The circuit for voltage- divider bias is shown in fig. (a) . The resistance  $R_1 \& R_2$  form a potential divider to apply a fixed voltage  $V_B$  to the base.

A resistance  $R_E$  has been connected in the emitter circuit. This resistance is not present in the fixed bias or collector to base bias circuits.

Fig. (a)

#### Analysis of Voltage divider bias circuit

#### **Base circuit**

The base circuit as shown in fig(b). Here we have considered collector & emitter terminals as open circuited. The base Voltage  $V_B$  is nothing but the voltage across resistor  $R_2$

i.e.

$$V_{B} = \frac{R_2}{R_1 + R_2} V_{CC}$$

This is because , current through R1 & R2 is approx. same and is equal to I.

#### **Collector circuit**

The collector circuit as shown in fig., the voltage across emitter resistance  $R_E$  can be as follows :

$$V_{E} = I_{E}R_{E} = V_{B} - V_{BE}$$

$$\therefore I_{E} = (V_{B} - V_{BE})/R_{E}$$

Applying the KVL to the collector circuit we get

$$-V_{CC} + I_C R_C + V_{CE} + I_E R_E = 0$$

$$\therefore V_{CC} = I_C R_C + V_{CE} + I_E R_E$$

$$V_{CE} = V_{CE} - I_E R_E - I_C R_C$$

#### **Bias stabilization**

- If  $I_c$  increases due to change in temp. or  $\beta$

- Then I<sub>E</sub> increases

- Hence drop across  $R_E$  increases ( $V_E = I_E R_E$ )

- But V<sub>B</sub> is constant. Hence V<sub>BE</sub> decreases.

- Hence I<sub>B</sub> decreases.

- Hence I<sub>c</sub> also deceases. Thus the compensation for increase in I<sub>c</sub> is achived.

#### Q.4. Draw the circuit diagram of Collector to base bias of a transistor. Explain its working.

Collector to base bias shown in fig. is also known as collector-feedback bias. Historically , this was another attempt at stabilizing the Q point. Again, the basic idea is to feed back a voltage to the base in an attempt to neutralized any change in collector current.

Like emitter-feedback bias circuit, collector feedback bias circuit uses –ve feedback in an attempt to reduce the original change in collector current.

#### Analysis

Applying KVL in the base circuit we have

$-V_{CC} + R_C(I_C + I_B) + I_B R_B + V_{BE} = 0$

$: I_{\rm B} = I_{\rm C}/\beta$  $: I_{\rm B} = \frac{V_{CC-V_{BE}}}{R_{C+R_B/\beta}}$

Similarly applying KVL on collector side

We have  $V_C = V_{CE} = V_{CC} - I_C R_C$

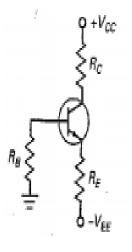

## Q.5. Draw the circuit diagram of two supply emitter bias of a transistor. Explain its working.

Sometimes electronic equipment has a power supply that produces both +ve and -ve supply voltages. The -ve supply forward biases the emitter diode. The +ve supply reverse bias the collector diode.

This circuit is derived from emitter bias, for this reason, we refer to it as two-supply emitter bias (TSEB).

#### Analysis

$V_B\approx 0~V$

Applying KVL from emitter to base loop in anticlockwise we have

$$V_{EE} - I_E R_E - V_{BE} = 0$$

$$\therefore - I_E = (-V_{EE} + V_{BE}) / R_E = (-V_{EE} + 0.7) / R_E$$

$$\therefore I_E = (V_{EE} - 0.7) / R_E$$

$$V(R_E) = V_{EE} - 0.7 V$$

Applying KVL on collector side we have

$- V_{CC} + I_C R_C + V_C = 0$

$$\therefore V_{\rm C} = V_{\rm CC} - I_{\rm C} R_{\rm C}$$

$$V_{CE} = V_C - V_E$$

#### Q.7. Compare Fixed bias, Collector to base bias & Voltage divider bias circuits.

| Sr.<br>No• | Parameter             | Fixed bias    | Collector to base<br>bias | Voltage divider bias                 |

|------------|-----------------------|---------------|---------------------------|--------------------------------------|

| 1.         | Emitter<br>Resistance | Not used      | Not used                  | Used                                 |

| 2.         | -ve Feedback          | Not used      | Included                  | Included                             |

| 3.         | Stability             | $S=(1+\beta)$ | $S = (1 + \beta) / [1 +$  | $S=(1+\beta) * [1+\frac{R_B}{R_C}]/$ |

|    | factor               |                                         | $\beta(\frac{R_C}{R_C+R_B})]$                      | $\left[1+\beta+\frac{R_B}{R_C}\right]$ |

|----|----------------------|-----------------------------------------|----------------------------------------------------|----------------------------------------|

| 4. | Q-Point<br>stability | Poor                                    | Moderate                                           | Good                                   |

| 5. | Configuration        | HAR | R <sub>B</sub><br>R <sub>C</sub><br>R <sub>C</sub> | $R_{1}$                                |

#### Numerical

Q.1. Determine  $I_C$ ,  $V_E$ ,  $V_B$ &  $V_C$  for the voltage divider configuration .If  $\beta=20$ ,  $R_1=62K\Omega$ ,  $R_2=9.1$  K $\Omega$ ,  $R_C=3.9$  K $\Omega$  $R_{\rm E} = 0.68 \text{ K}\Omega \& V_{\rm CC} = 16 \text{ V}$ Exp: As the biasing is voltage divider We have  $V_B = V_{CC}$ .  $R_2/(R_1+R_2)$   $\therefore V_B = 16 \text{ x } \frac{9.1k\Omega}{62k\Omega+9.1k\Omega} = 2V$  $:: V_E = V_B - V_{BE}$  $: V_{\rm E} = 2V - 0.7V = 1.3V$  $:I_E = V_E / R_E$  $\therefore I_{E} = 1.3 V / 0.68 K \Omega = 1.23 mA$  $: I_{C} = \alpha . I_{E} = \beta / (\beta + 1) I_{E}$  $\therefore$  I<sub>C</sub>= 1.23mA x 20/21 = 1.17mA Q.2.  $R_B = 240 \text{ K}\Omega$ ,  $R_C = 2.2 \text{ K}\Omega$ ,  $V_{CC} = 12 \text{ V}$  &  $\beta = 50$ Exp: As it is fixed bias

For the fixed bias circuit determine IB, IC, VCE, VB, VC&VBC for the following parameters

We have  $I_B = (V_{CC} - V_{BE})/R_B$  $\therefore$  I<sub>B</sub>= (12-0.7)/240 KΩ  $= 47.08 \mu A$  $:: I_C = \beta I_B$  $\therefore$  I<sub>C</sub>= 50 x 47.08µA = 2.35mA  $:: V_{CE} = V_{CC} - I_C R_C$  $::V_{CE} = 12 - 2.35 \text{mA x } 2.2 \text{ K}\Omega$ = 6.83 V : Emitter terminal is grounded ...  $V_{B} = V_{BE} = 0.7V$  $V_{C} = V_{CE} = 6.83 V$  $::V_{BC} = V_B - V_C$

$$\therefore V_{BC} = 0.7V - 6.83V = 6.13 V$$

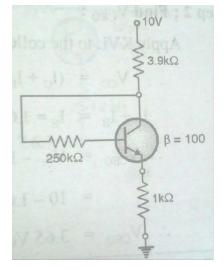

#### Q.3. Determine the values of $I_C \& V_{CE}$ for the biasing circuit shown in fig.

Exp: As per the given parameters in Collector-emitter feedback

Applying KVL on input side, we have

$$\begin{split} -10 + 3.9 k\Omega (I_C + I_B) + 250 k\Omega. \ I_B + V_{BE} + \ 1 \ k\Omega. \ I_E = 0 \\ & \because I_E = (1 + \beta) I_B \ , I_C = \beta I_B \ , V_{BE} = 0.7 \ \text{ and } \beta = 100 \\ & \therefore \ -10 + 3.9 k\Omega (\beta I_B + I_B) + 250 k\Omega. \ I_B + 0.7 + \ 1 \ k\Omega. \ (1 + \beta) I_B = 0 \\ & I_B = 9.3 / \ [3.9 k\Omega (1 + \beta) \ + 250 k\Omega + 1 \ k\Omega \ (1 + \beta)] \\ & I_B = 9.3 / \ [3.9 k\Omega (1 + 100) \ + 250 k\Omega + 1 \ k\Omega \ (1 + 100)] \\ & I_B = 12.48 \ \mu A \ Ans \end{split}$$

Q.4. Determine the voltage gain of a single stage CE transistor if the effective resistance of collector circuit is  $2k\Omega$ , input resistance is  $1k\Omega$  & current gain is 50. [Important]

Exp: Given  $R_C = 2k\Omega$ ,  $R_{in} = 1k\Omega$  &  $\beta = A_i = 50$

$$\therefore A_{\rm V} = \beta \frac{R_L}{R_{in}}$$

$$\therefore A_{\rm V} = 50 * \frac{2 \mathrm{k} \Omega}{1 \mathrm{k} \Omega} = 100 \text{ Ans}$$

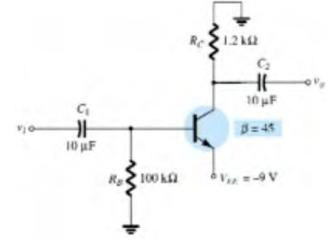

#### **Q.5.** Determine $V_C$ and $V_B$ for the network of Fig.

Exp: Applying KVL in the anticlockwise for the base-emitter loop, we have

$$V_{C} = - I_{C} R_{C}$$

∴V<sub>C</sub> = - 3.735 mA x 1.2 kΩ = -4.48 V ∴V<sub>B</sub>= - I<sub>B</sub> R<sub>B</sub> ∴V<sub>C</sub> = -83mA x 100 kΩ = -8.3 V

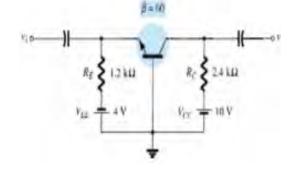

## Q.6. Determine the voltage $V_{CB}$ and the current $I_B$ for the common-base configuration for the given fig.

Exp: Applying KVL to the input circuit yields

$$-V_{EE} + I_E R_E + V_{BE} = 0$$

$$\therefore I_E = (V_{EE} - V_{BE}) / R_E = (4-0.7) / 1.2 \text{ k} \Omega = 2.75 \text{ mA}$$

Applying KVL to the output circuit yields

$$-V_{CC} + I_C R_C + V_{CB} = 0$$

$$\therefore V_{CB} = V_{CC} - I_C R_C$$

$$\therefore I_C \approx I_E$$

$$\therefore V_{CB} = 10 - 2.75 \text{ mA x } 24 \text{ k} \Omega = 3.4 \text{ V}$$

$...\,I_B{=}~$  2.75mA/  $60=45.8\mu A$  Ans

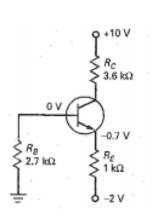

#### Q.7. What is the collector voltage in the given circuit

Exp: Applying KVL at the Emitter base terminal we have

+ 2V − 1k Ω x  $I_E - V_{BE} = 0$   $\therefore I_E = (2 - 0.7) / 1k Ω = 1.3mA$   $\therefore V_C = V_{CC} - I_C R_C$ Also  $I_C \approx I_E$   $\therefore V_C = 10 - 1.3mA x 3.6k Ω$ 5.32 V Ans